Introducing TI MSP430 Microcontrollers

|

|

Texas Instruments (TI) is a well-known US-based semiconductor manufacturer. TI is perhaps best known to many as the manufacturer of some of the fanciest scientific calculators in the market. Of the long list of electronic devices produced by TI, microcontrollers are on the top. TI manufactures some of the coolest and advanced microcontrollers of the market today. There are several categories of micros from TI. These include general purpose low power MCUs which mainly comprise of MSP430s, ARMs like TM4Cs, MSP432s, etc, micros for wireless communications like CC2xxx series, ARM + DSP micros, DSP-specialized micros like the TMS32xxx series and so on. It will look as if TI is committed toward mixed signal microcontrollers that are engineered for highly sophisticated industrial challenges. This issue will cover an insight of value-line MSP430 general purpose micros.

MSP430s are not seen as much as the popular 8051s, PICs and AVRs. In most of the Asian market, for example, MSP430s are rare when compared to other microcontrollers and even still rare when compared to other chips produced by TI itself. I don’t know why there is such an imbalance. Perhaps one big reason is its inclination towards low power consumption and limited resources. Low-power means that these MCUs are crafted for special low power applications unlike most other micros. Secondly TI micros are a bit expensive than other micros. Despites these, TI has provided some great tools for making things simple. You can get your hands on some cool MSP430 chips through some affordable Launchpad boards and still it worth every penny learning MSP430s. Firstly, it is a family of ultra-low power high performance 16-bit (16-bit data bus) micros which are unlike the popular 8-bit platforms. Secondly MSP430s have highly rich internal hardware peripherals that are second to none. For instance, MSP430s can be operated over a wide voltage and frequency ranges. Another great feature that is less common in most 8-bit micros is the DMA controller. Fortunately, MSP430s possess this. Probably it is your first such micro family that is somewhere between 8-bit and 32-bit micros. In the end, MSP430s will surely give you a taste of absolute American technology and concepts.

The MSP430 Family

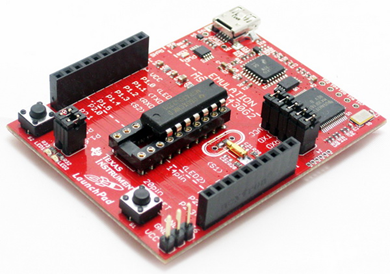

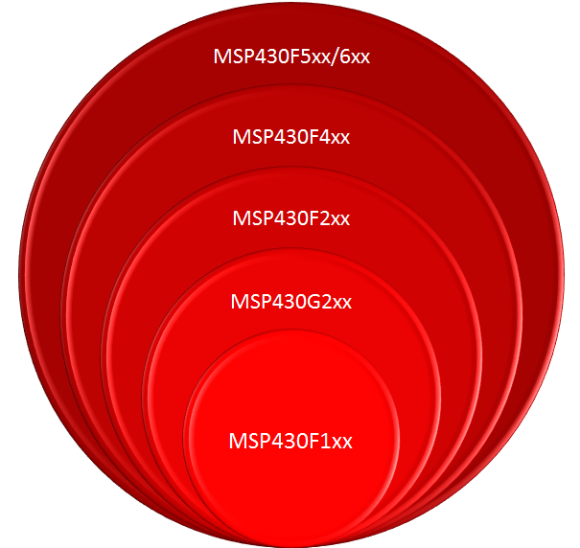

Shown below is the family tree of MSP430 series microcontrollers from TI.

The most common MSP430 micros are the MSP430FR series, MSP430F series, MSP430G series and the newly introduced MSP432 series.

MSP430FR series micros mainly feature high reliability, high endurance, 10-year data retention non-volatile FRAM (ferroelectric random-access memory) memories. This series offer 16-bit solutions for ultra-low-power sensing and system management in areas like smart building management systems, smart grids, military and industrial designs. They feature the lowest standby power consumption of about 350 nA with RTC, 100 µA/MHz active power consumption and the unique ability to save and instantly restore system state right after power failures.

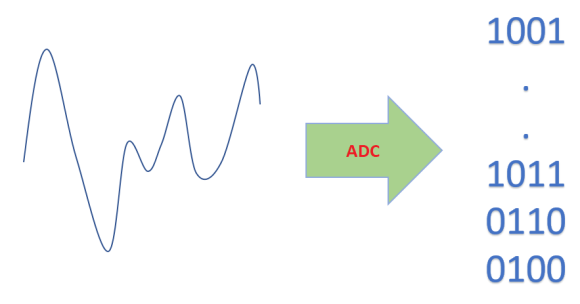

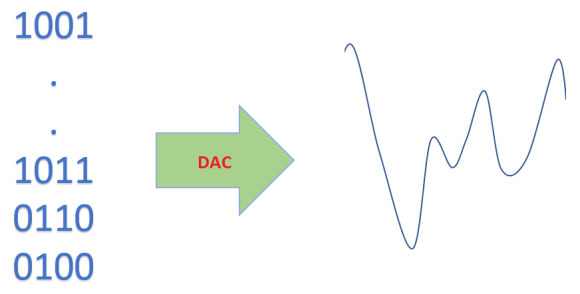

MSP432 series micros are the perfect combinations of MSP430 low-power portfolio with advanced mixed-signal features and the high-performance processing capabilities of 32-bit ARM M4F engine. These micros have high measurement precisions and contain high performance peripherals like high resolution differential ADCs, DMA, IOT connectivity, etc. This series fills the gap between 16-bit MSP430s and 32-bit ARM architecture and as of this moment this series is the most recent development in the MSP430 family.

CC430 series is a small series of MSP430s with almost all features one can find in a typical MSP430 micro and embedded sub-GHz radio transceivers. They are well-stuffed true System-on-Chip (SOC) solutions that remove the necessity of additional off-board wireless solutions.

Yet another tiny series of MSP430 micros include MSP430Cxx and MSP430Lxx micros. These micros are intended for extreme low voltage (0.9 – 1.65V) operations. With just one Nickel Cadmium (NiCd) battery it is possible to run any micro of this series. They feature low resolution analogue frontends and low pin counts.

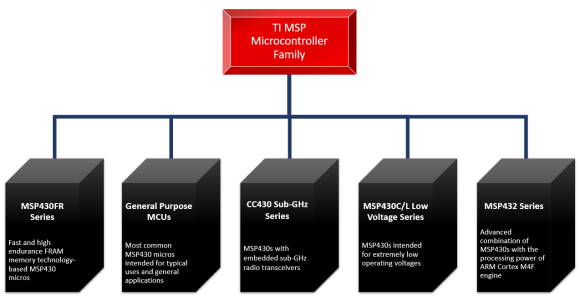

The only series that is left to be discussed is the general purpose MSP430s series microcontrollers. By general purpose, it is meant that these micros can be use in almost any scenario. It is this series of micros that we will be dealing here. The table below summarizes this family:

For now, don’t struggle to understand the abbreviations of this table. You’ll eventually know about them as we proceed.

Note that there are some other MSP430 devices that are not accounted here. These devices are either rare or subset of the mentioned families. If you want to know more about MSP430 microcontrollers then you can go through the following Wikipedia article: https://en.wikipedia.org/wiki/TI_MSP430.

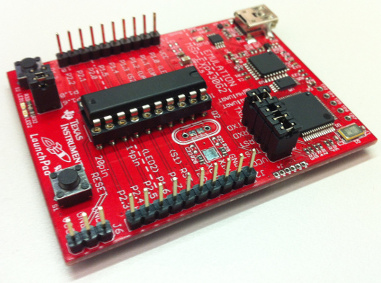

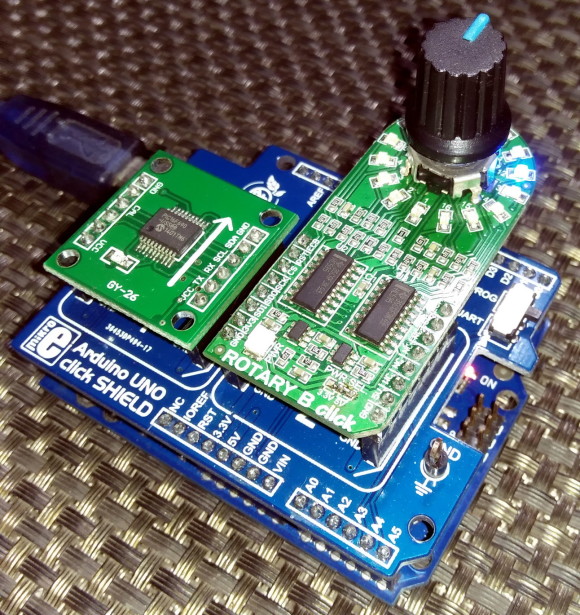

Launchpad Boards and BoosterPacks

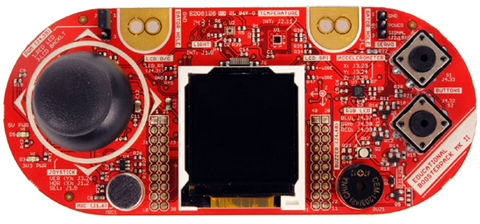

Launchpad boards are affordable MSP430 evaluation kits. For just few dollars, you can have your own Launchpad boards. They are so cheap that an average school-going student can afford one with his/her own pocket money. However, this cheapness doesn’t compromise quality nor performance. They are more-or-less alike Arduino boards in terms of board size and on-board resources except they don’t share same pin naming conventions and board layouts. Well that’s not a big issue. However, it would have been better if the Launchpads shared Arduino-like form factor. This would have enabled using Arduino shields with Launchpads. TI has, however, its own brand of shields called BoosterPacks and they seem to like promoting their own idea, owing to which there’s still no official TI Launchpad that share exactly Arduino form-factor/shape. It is a very aggressive marketing boldness. Shown below is the BOOSTXL-EDUMKII BoosterPack. It is just like Arduino Esplora with lots of on-board sensors and devices except for the MCU. It is good for game development and sensor applications. There are other useful BoosterPacks dedicated for capacitive touch, displays and so on.

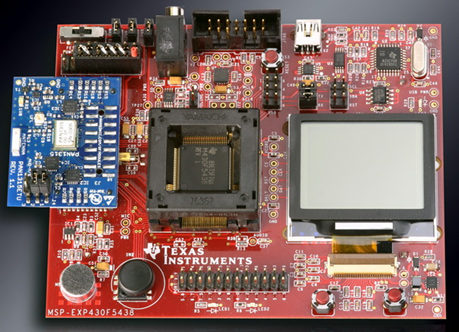

Launchpad boards are not the only development boards offered by TI. There are many other dev boards too. Shown below is the TI MSP-EXP430F5438 Bluetooth platform development board.

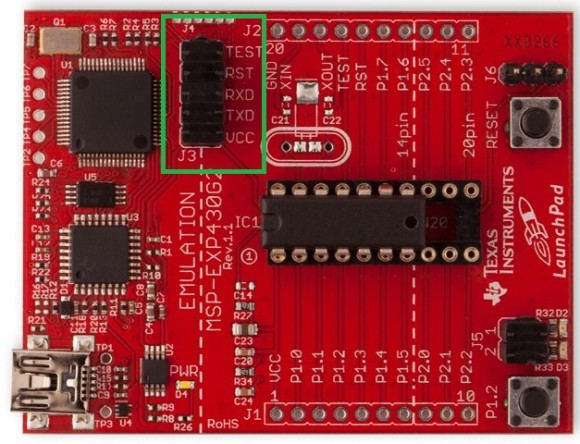

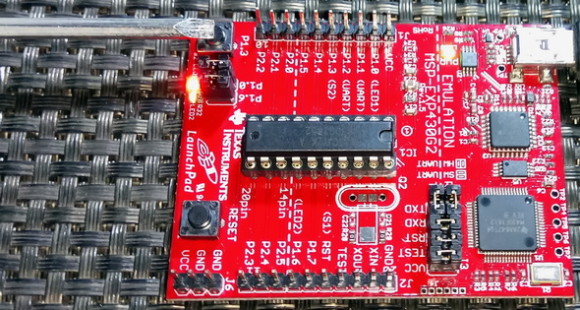

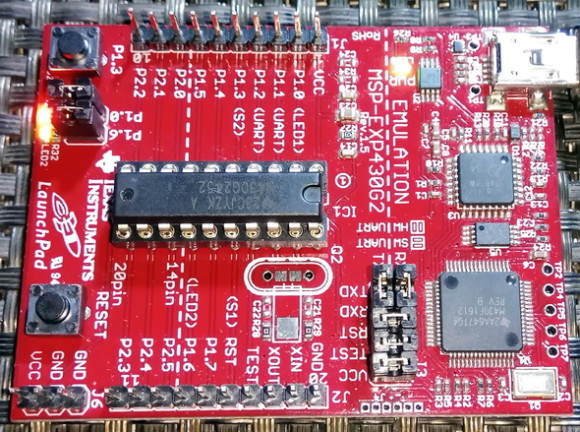

However due to cheapness and relatively good availability Launchpad boards are by far most popular, particularly the MSP-EXP430G2 Experimenter’s Launchpad board.

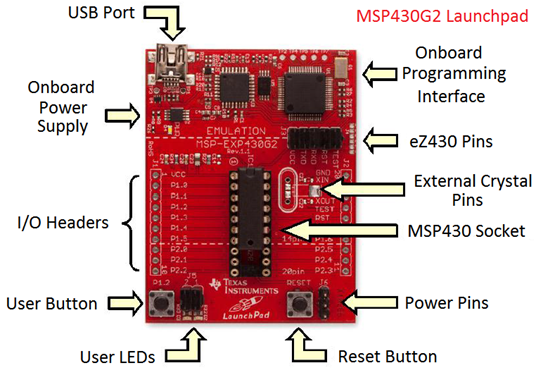

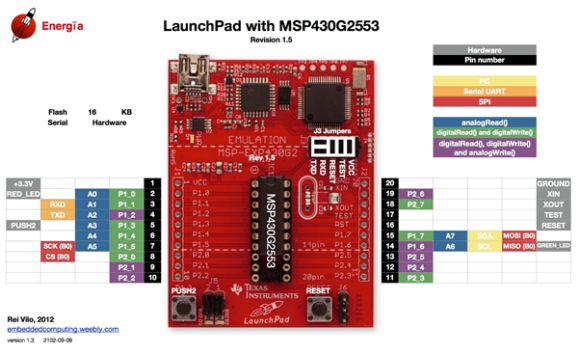

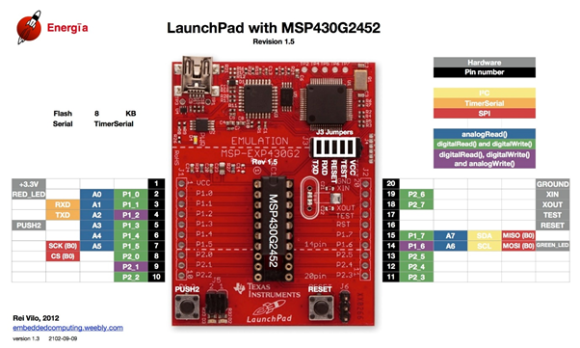

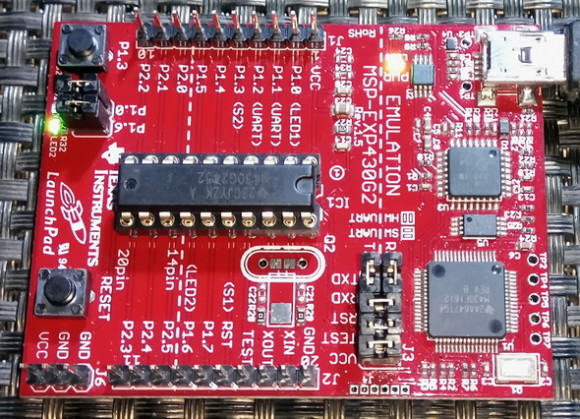

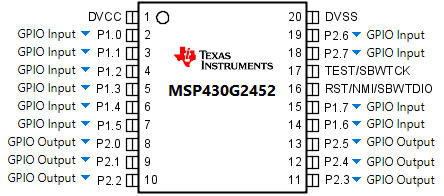

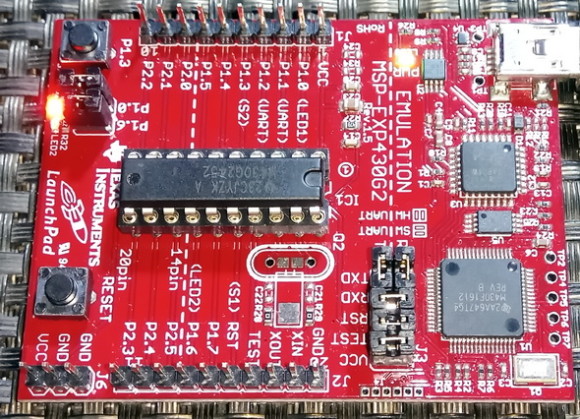

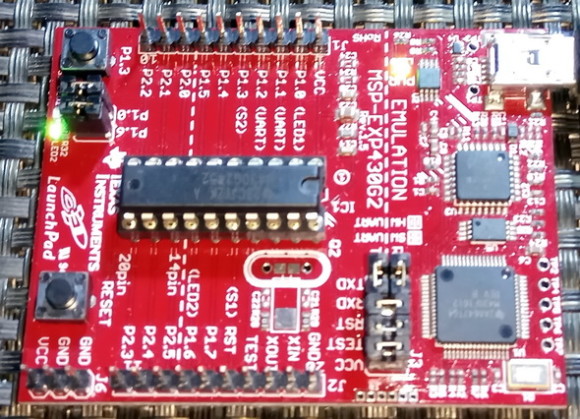

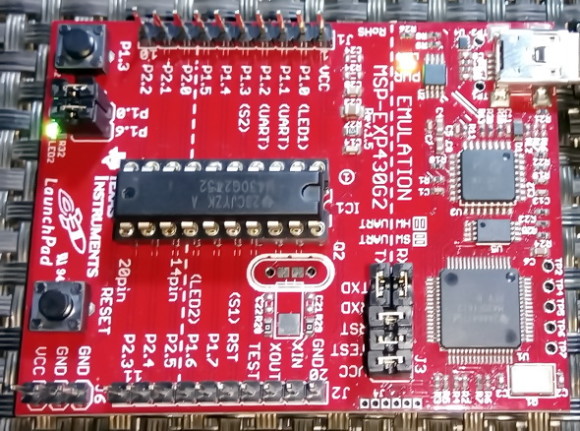

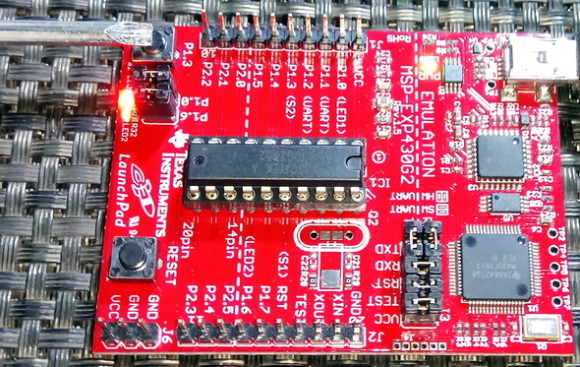

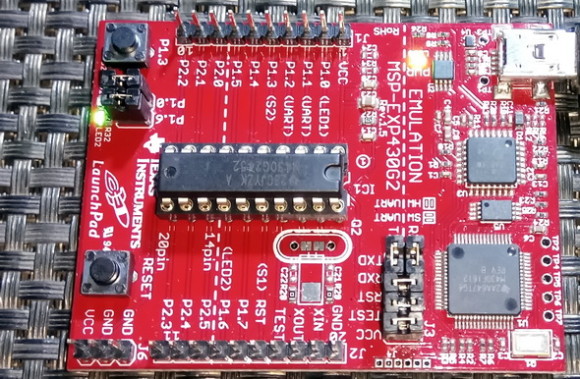

This board comes boxed with two micros – MSP430G2452 and MSP430G2553. Both of these mixed-signal MCUs come in PDIP packages. We can take them off from the board and use them in bread boards, strip boards, PCBs, etc. Shown below is the layout of a MSP-EXP430G2 Launchpad board.

Just like any other evaluation kit, every Launchpad comes embedded with user LEDs, buttons, I/O port headers (also known as BoosterPack connectors), onboard power supply, USB-to-serial converter and programming interfaces.

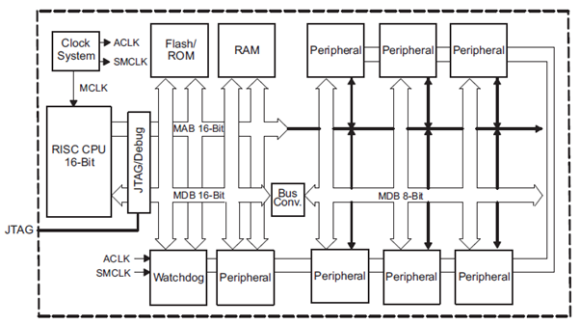

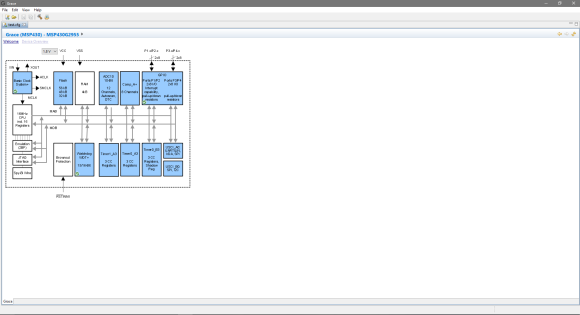

MSP430s are ultra-low power 16-bit general purpose microcontrollers. A MSP430 micro consists of a 16-bit RISC CPU, wide variety of feature-rich peripherals and a flexible clock system all under the hood of a von-Neumann architecture. Because of their ultra-low energy consumption profile, MSP430s are well-suited for battery/solar powered/limited or renewable energy applications.

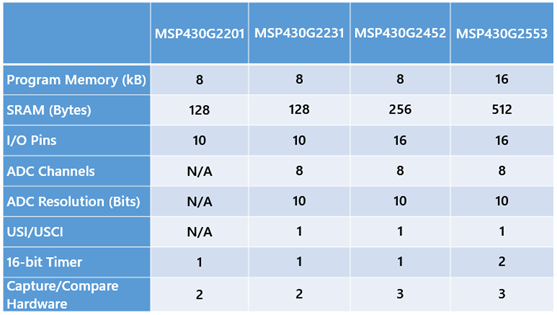

MSP430G2452 and MSP430G2553 are both almost identical in terms of hardware peripherals and pin count. MSP430G2553 has some additional hardware features like more RAM-ROM memories, timers and USCI-based hardware interfaces for LIN and IrDA communications.

Shown below is a comparison table of some common MSP430 chips usually found with Launchpad boards.

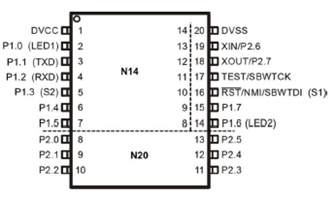

Other Launchpad boards contain other chips but fortunately they share the same pin layout and so they are fully pin compatible. The fourteen pin parts and twenty pin parts share the same pin layout as shown below:

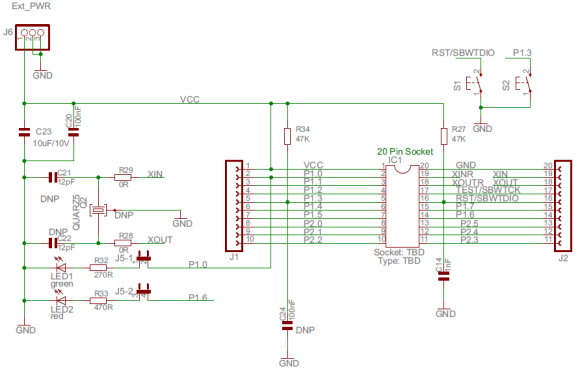

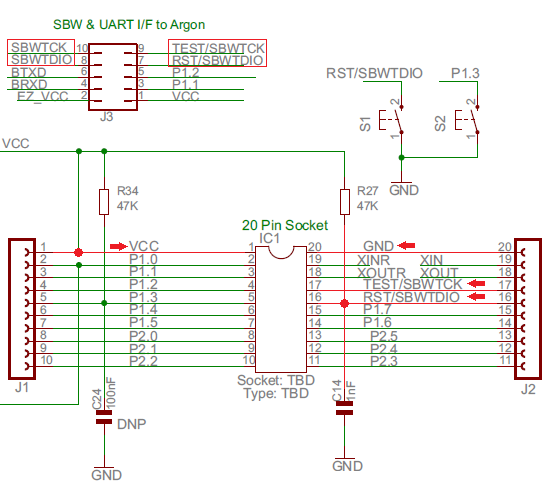

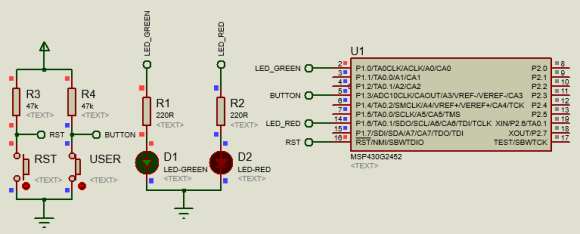

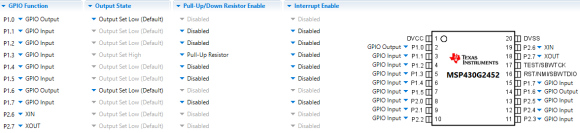

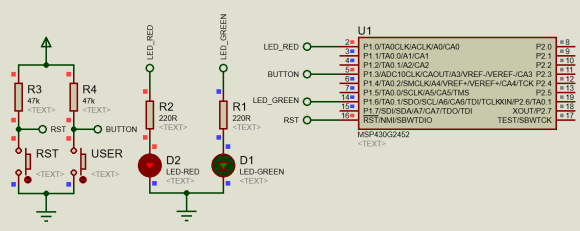

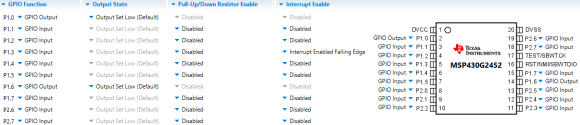

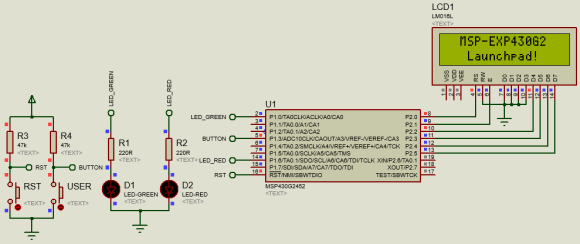

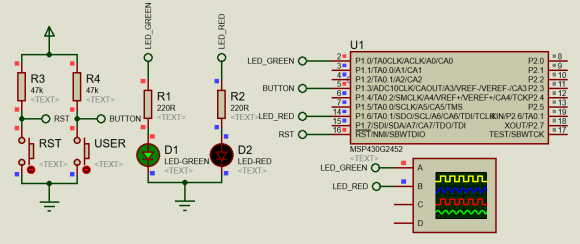

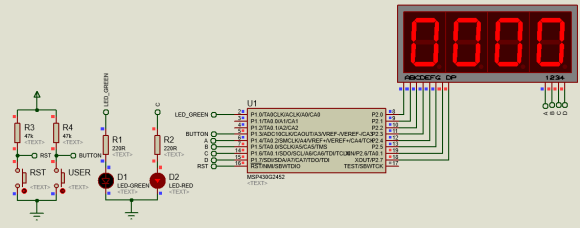

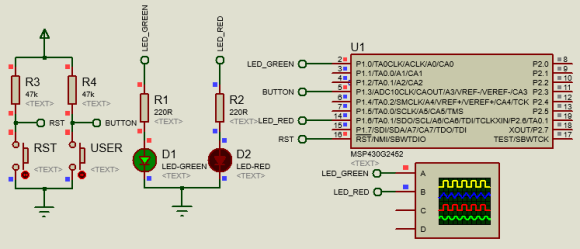

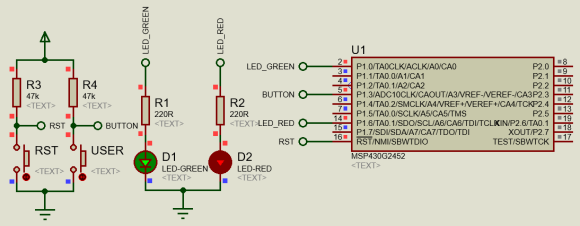

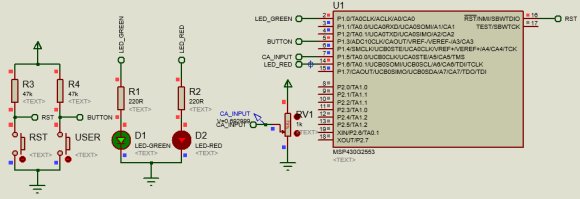

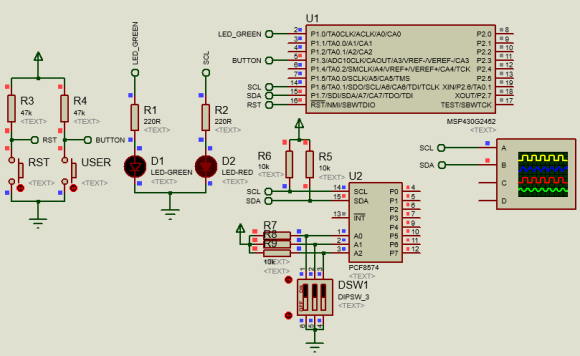

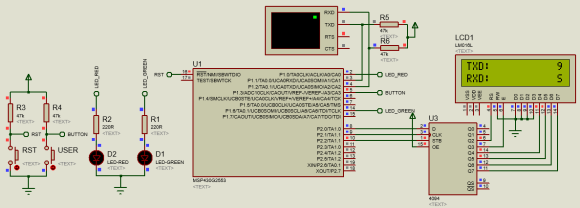

Though the pin names are labelled properly on the silkscreens of the boards, it is sometimes necessary to check the schematic for details. Shown below is the basic schematic of a MSP-EXP430G2 Launchpad.

From the schematic, we can see what has been placed on the board by default. Parts labelled DNP are not placed on a fresh Launchpad board. These have been left for the users.

If these don’t matter much and you need something simpler, then there are Arduino-like pin maps for Launchpads. Though they are made for Energia IDE, they are useful for quick overviews.

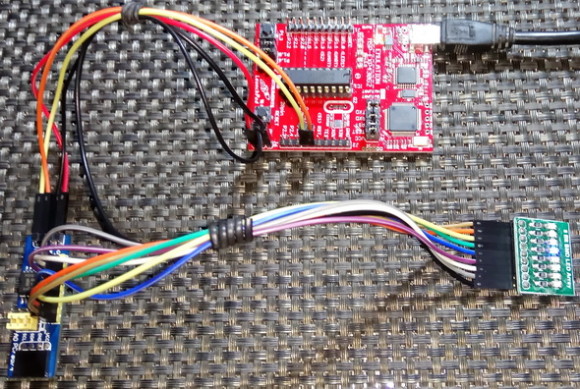

Hardware

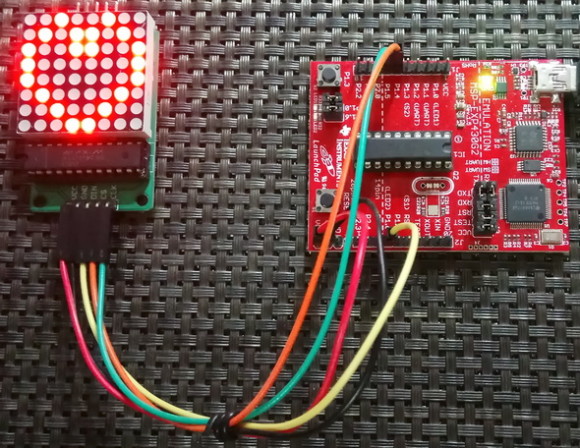

We will obviously need a MSP430 Launchpad board. For this tutorial, I used MSP-EXP430G2 Launchpad board with MSP430G2553 and MSP430G2452 microcontrollers.

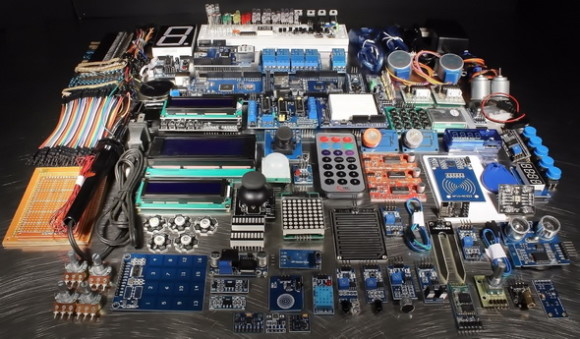

Apart from the Launchpad board, we will need basic tools like a digital multimeter (DMM), wires or jumper cables, a power bank and other stuffs typically available in an Arduino starter kit like the RIASpire one shown below.

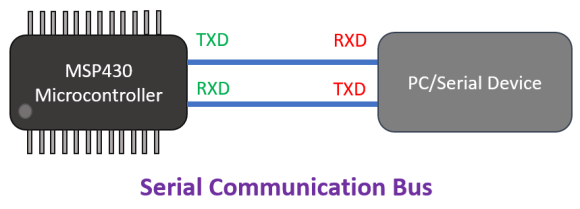

An additional external or off board programmer/debugger is not needed since MSP430 Launchpad boards come with on board Spy-Bi-Wire (SBW) programming/debugging interface. This interface utilizes pins labelled TEST and RST apart from power pins and so only four wires are needed. Note reset pin should be externally pulled up. Check the diagram below.

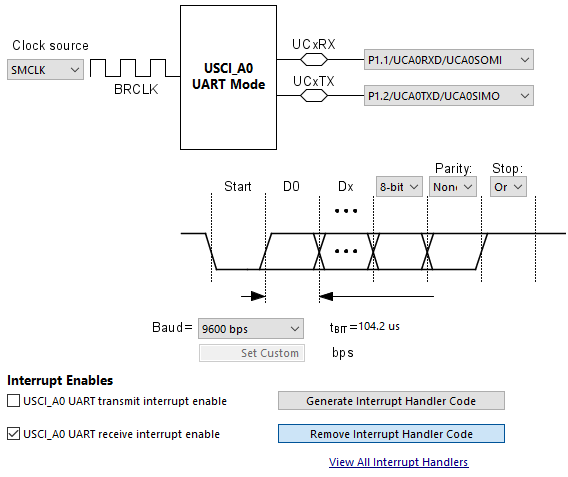

Similarly, we don’t need to buy/use any external USB-serial converter for serial communication as the boards come with onboard hardware for this communication.

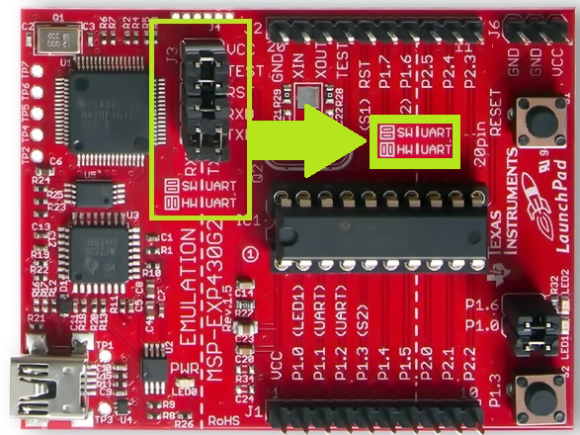

In all Launchpad boards, there are headers with jumpers as shown below to separate onboard programmer from the target. This allows us to use a Launchpad board as standalone programmer. We can also detach it. The top dotted line marks the border between the target and the programmer.

It is still nice to have one external MSP-FET programmer. FET stands for Flash Emulation Tool and it supports both JTAG and SWD interfaces. FETs are pretty expensive tools.

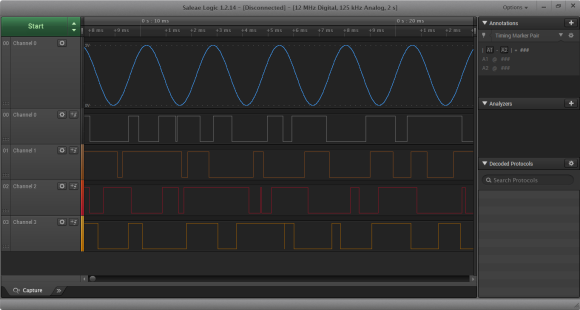

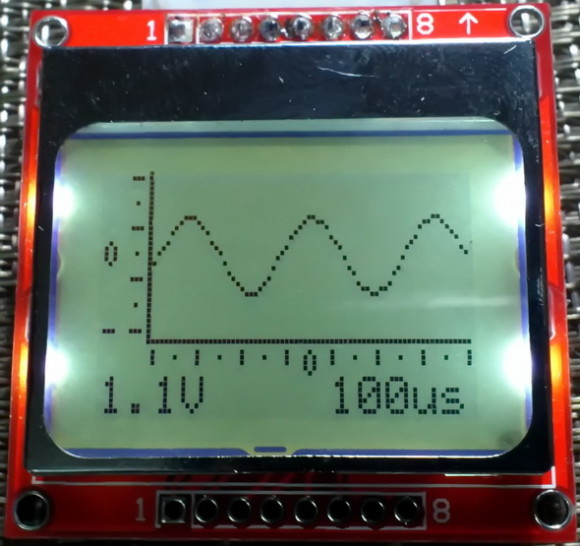

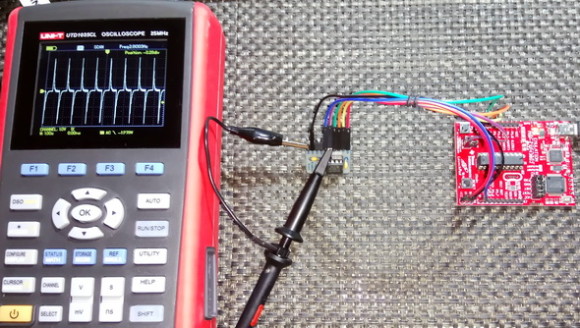

Lastly, I strongly recommend having an oscilloscope or a logic analyser for checking signals and timing-related info. In many cases, informations provided by these tools become extremely necessary.

Software

There are numerous ways of learning and using a new microcontroller family effectively. A number of C/C++ compilers are available for coding MSP430 micros. Hobbyists and novice users find Arduino-like solutions easy and quick but from an engineer’s perspective such solutions are inexplicably incapable of extracting the sweet fruits of a well-armed microcontroller. Rawer approaches are preferred by professionals but they too seek reduced efforts and quick solutions. The learning curve is also needed to be a smooth one. In this segment, we will checkout some common software solutions for MSP430s.

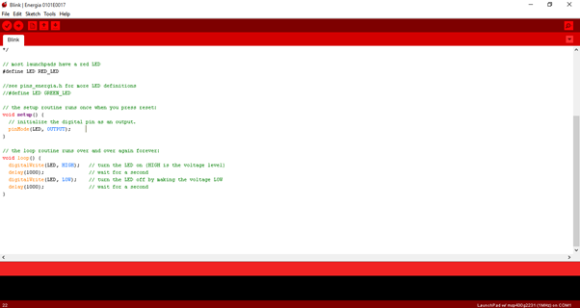

Firstly, there is the free open-source Energia IDE. This is an Arduino-like IDE that enables users to code MSP430s in the Arduino way. It supports many Launchpad boards including those which are based on ARM cores. I have used it a lot and it is fun using it for simple hobby projects. However, I wanted to harness the true power of MSP430s. As with Arduino, you can access MSP430 registers in Energia too but that doesn’t make significant differences in terms of coding efficiency and memory consumptions. Energia has the same issues as with Arduino. Arduino framework on top of an AVR makes it much less robust when compared to a crude AVR. The same thing applies for Energia too. Another key limitation of Energia is the fact that not all MSP430 chips are supported by it. Energia is, however, very easy to use, quick and useful for rapid prototyping or testing. The costs are low overall efficiency and larger code size. Just like Arduino, Energia is not well-suited for highly sophisticate professional projects. It is just a rapid prototyping tool that we can use to check a proof-of-concept but not the right tool to build that concept. A smaller hammer is useful for nailing a pin but it is not the perfect tool for breaking a giant boulder.

Energia is available at http://energia.nu/.

Please note that Energia is not supported by the Arduino LCC which means it not developed or maintained by the guys from the Arduino team. This doesn’t matter much for its users. However, the IDE is not frequently updated like the Arduino IDE.

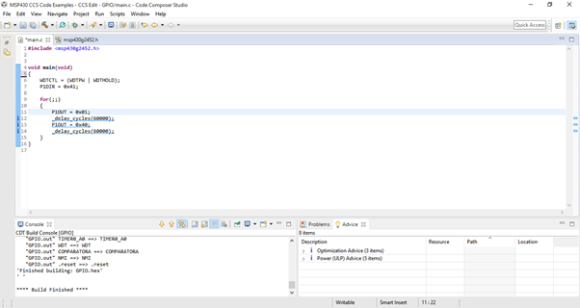

Next, we have TI’s own compiler – the Code Composer Studio (CCS). CCS is a C/C++ compiler based on Eclipse IDE. CCS comes with TI’s proprietary compilers that are best in code optimization. Those who have used Eclipse-based IDEs before know the advantages Eclipse framework brings with it. It has an excellent code navigation system, perspective views, refactoring, etc. CCS compiler comes with all of these stuffs and many more like debugger interface and TI App Store. Apart from all these there are some helpful cloud-based tools from TI. This tutorial is based on CCS compiler. It is free for download from TI’s website – http://www.ti.com/tool/ccstudio. Make sure you have a TI account.

Then there is IAR compiler. I have never used IAR products but I have heard from many that it is very popular and widely used. However, it is expensive too.

Lastly, like for many other platforms we have the free open-source GCC compiler for MSP430s. MSP430 GCC can be integrated with CCS IDE.

We will see during coding that compilers don’t make significant differences in coding style, making codes cross-platform compatible. I also intend to keep things simple and quick. This is why I focus on tools rather than other stuffs. With right set of tools, any issue can be addressed decently and rapidly.

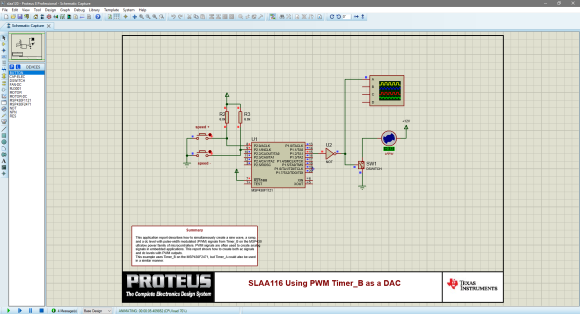

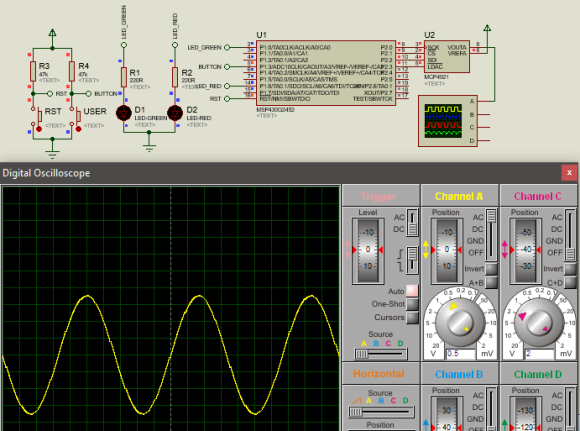

Additionally, some more software tools are needed for supportive purposes. Proteus VSM is a good interactive simulator cum PCB design software. Luckily it supports MSP430 micros. However, it is very expensive unless you are using a pirated version of it. Frankly speaking, I have never advocated for simulations because simulations do not address the real-world challenges we encounter in a real-life real-time project. Simulations, for example, cannot simulate real-world environment conditions nor can they emulate situations which result in “hang”-like stuck up conditions. Simulations don’t take the effect of noise and electromagnetic disturbances into account. Additionally, sometimes simulations give wrong results. I have spent many wasted hours trying to debug an issue with simulation only to find out that the simulation was incorrect. Still however, simulations are helpful in some special cases. For instance, when designing a LCD menu, simulation is a time and effort saver. Personally, I recommend and use real-world debugging over simulations. This gives me a lot of confidence.

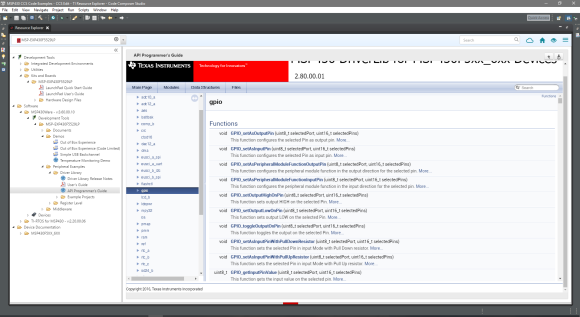

The coolest stuffs for MSP430s are TI’s MSP430Ware driver libraries (driverlib) and GRACE. Driver libraries remove the pain of traditionally coding MSP430s using registers. Driver libraries provide easy-to-use API functions for configuring MSP430 peripherals just like the Standard Peripheral Libraries (SPL) of STM8 micros. However, these libraries are only supported for the newest and resource-rich MSP430 microcontrollers like the MSP430F5529LP. This idea of driver libraries is quickly gaining mass popularity and is becoming standard day-by-day for all modern era micros. MSP430Ware can be downloaded for free from http://www.ti.com/tool/mspware.

You can use TI’s Resource Explorer to check out what’s in driverlib and if your target MCU is supported.

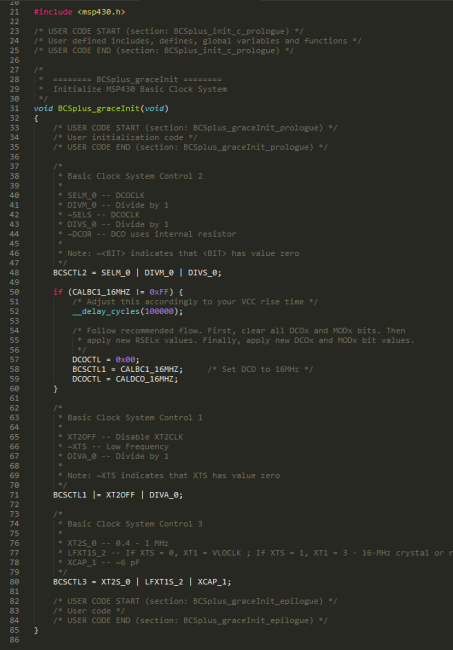

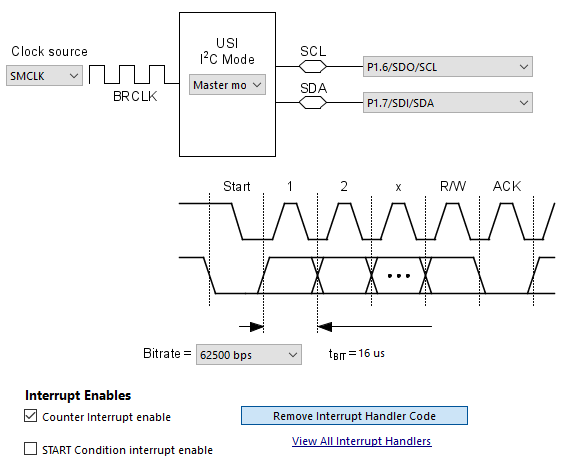

GRACE, on the other hand, is intended for relatively less-resourceful micros like the MSP430G2231 that are mostly well-suited for lower level assembly language environments. GRACE is basically a graphical code generator tool, much like the STM32CubeMX that can be used to generate setup configuration codes for MSP430F2xx, MSP430G2xx and some FR series micros. However, GRACE only generates register values for small MSP430 micros. For large and advanced MSP430 micros driverlib-based codes are generated instead of register-level codes. The rest is just like coding any other microcontroller. Throughout this tutorial, GRACE has been used for all demos.

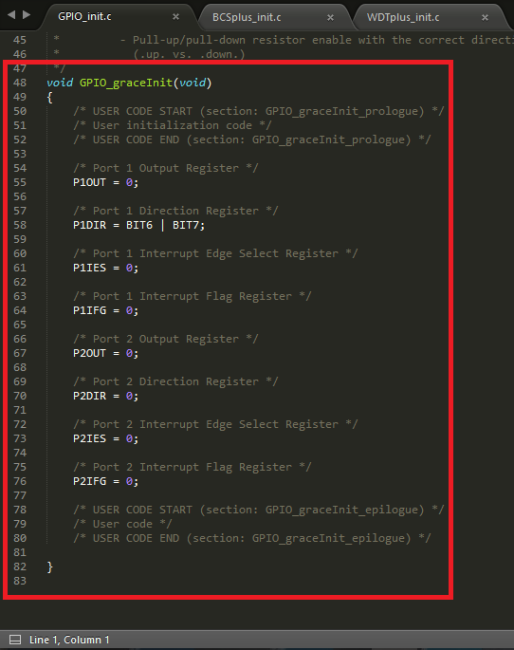

As we can see the generated code snippet sets appropriate registers as per our setup in GRACE GUI.

GRACE can be downloaded without any charge from TI’s website: http://www.ti.com/tool/GRACE?keyMatch=grace%203&tisearch=Search-EN-Products.

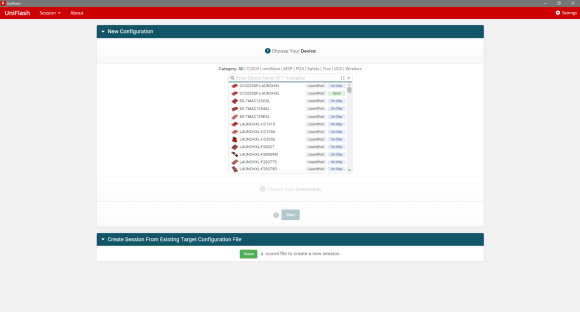

We will also need a separate standalone programmer GUI tool. Why? Because it looks totally stupid to open the heavy CCS software every time to upload a code to a new target after having built the final code for it. For this purpose, we will need UniFlash programmer GUI.

UniFlash can be downloaded from http://www.ti.com/tool/uniflash or can be accessed via TI cloud.

Additionally, I recommend using Sublime Text (https://www.sublimetext.com/3) or Notepad++ (https://notepad-plus-plus.org/download/v7.4.2.html) as a code viewer/editor.

Make sure you also downloaded Launchpad board drivers from here: http://www.ti.com/lit/sw/slac524/slac524.zip.

Documents, Pages and Forums

The following documents must be acquired:

- Device Datasheet

This write up covers MSP430G2452 and MSP430G2553 microcontrollers and so we will be needing the datasheet of these microcontroller for technical specs and characteristics. These can be found in the following links:

http://www.ti.com/lit/ds/symlink/msp430g2452.pdf

http://www.ti.com/lit/ds/symlink/msp430g2553.pdf

If you are using some other microcontroller then you must acquire its datasheet first.

- Reference Manual

MSP430x2xx reference manual covers the details of all the hardware available in this family of microcontrollers. Unlike other microcontrollers, datasheet of a MSP430 micro, only says about technical specs and characteristics. Reference manuals say about internal hardware, how to use them and about internal registers. This is the most important document of all.

http://www.ti.com/lit/ug/slau144j/slau144j.pdf

- Launchpad User Manual and Associated Files

Visit the following link for Launchpad board user manual and other docs:

http://www.ti.com/tool/msp-exp430g2. This document not just introduces the Launchpad board, it also contains schematics, layouts and other stuffs. Off all the stuffs in the user manual, Launchpad board’s schematic is the most valuable thing.

- App Notes.

Though not mandatory, having a collection of MSP430 application notes is a surplus. These show various ideas and design concepts. Visit TI’s website for these docs.

There are some important websites, online communities and forums that are very helpful. Some of the most popular ones are:

https://e2e.ti.com/support/microcontrollers/msp430/

http://processors.wiki.ti.com/index.php/Main_Page

http://www.ti.com/lsds/ti/microcontrollers-16-bit-32-bit/msp/overview.page

http://www.ti.com/lsds/ti/tools-software/launchpads/overview/overview.page

Starting a New CCS Project

Beginning a new CCS project is not too complicated. Provided that CCS is installed in your PC, simply run it.

In just a few seconds, CCS’s logo splashes.

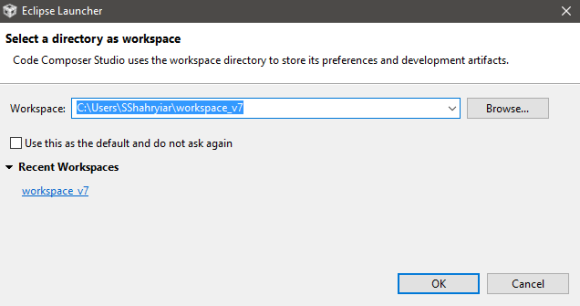

You’ll be asked for workspace location. Either select an existing workspace if you have one or create a new one.

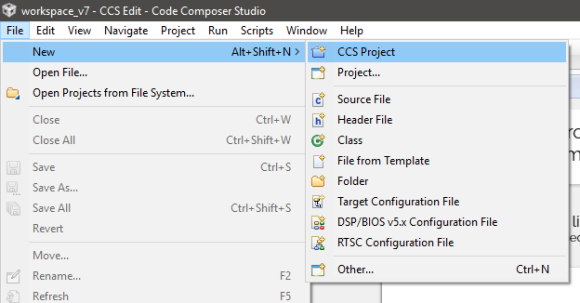

Next click File >> New >> CCS Project.

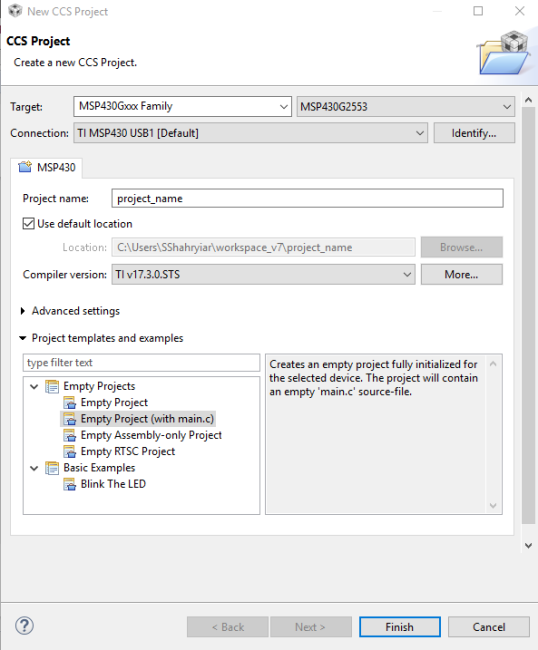

The following window will show up then:

Here we just need to setup target MCU, name of the project, compiler version and project type. Keep other options unchanged unless you are sure of your actions.

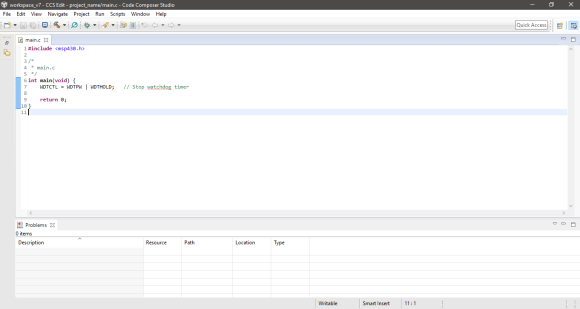

The following window appears after hitting the finish and we are good to go for coding. It is just that simple.

One advice I would like to give here, never delete any workspace file or folder unless you created it. It is possible to rename and remove projects from CCS IDE.

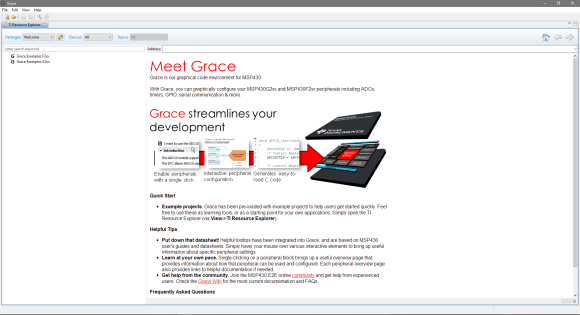

GRACE

As stated earlier, GRACE is a graphical configuration tool. It reduces the effort of thoroughly reading datasheets and reference manuals. I highly recommend using it no matter if you are novice or expert.

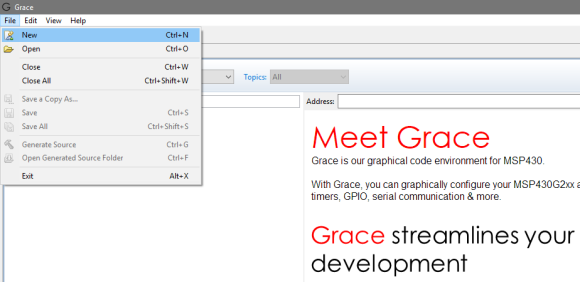

First run GRACE.

Wait for it to launch.

TI’s Resource Explorer kicks in on first start up. It may not do so every time though.

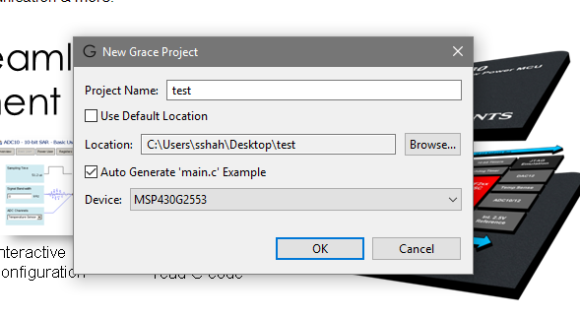

Click File >> New to begin a new GRACE project.

You’ll be prompted for project location, MCU part number and project name as shown below:

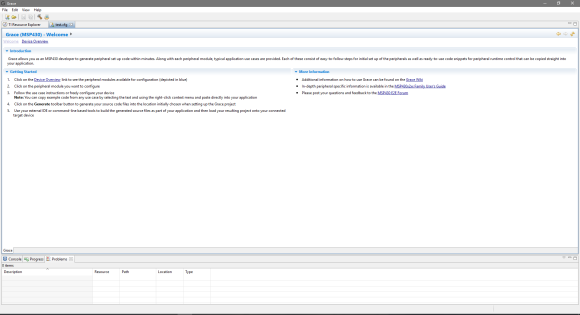

Once all the parameter fields are filled, we are ready to configure our target MCU. A welcome screen shows up next.

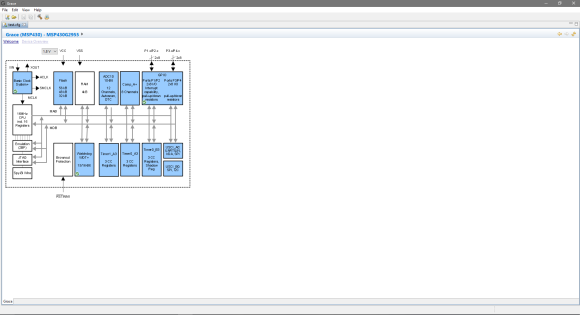

From the welcome screen, we have to click on Device Overview and get an insight of the device’s peripherals as peripheral blocks.

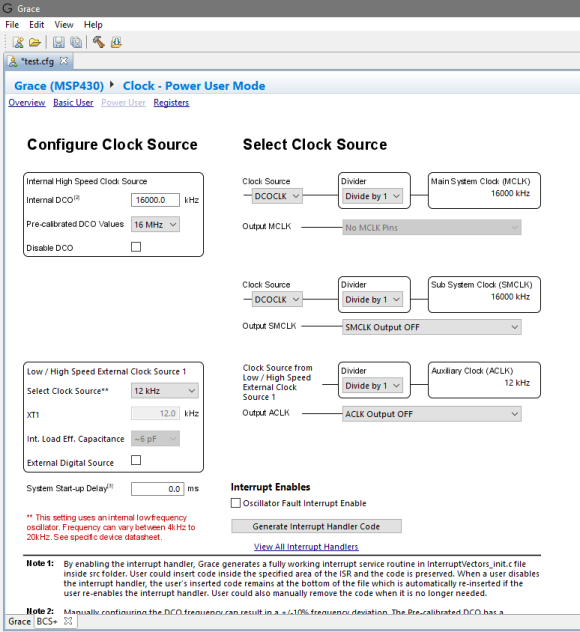

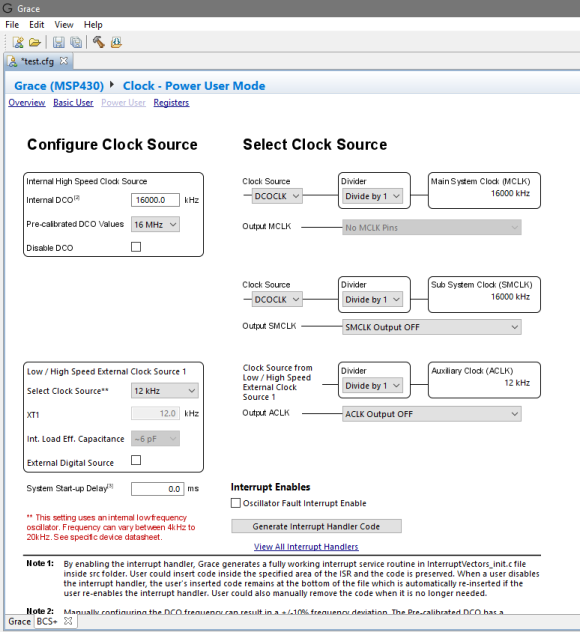

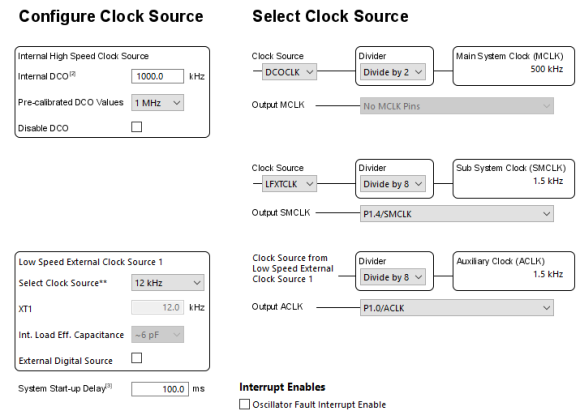

We can now click desired hardware peripheral block (blue blocks) to check what features and code examples it offers and set it up as required. There are two types of setups for all modules – Basic and Power users. Basic User setup is for simple setup when you don’t know everything of a peripheral in details and don’t want to mess things up. Power User setup is for expert users with more advanced options. Shown below are the Power User options for setting up the clock system:

After setting up everything, just hit the hammer or Build button and the configuration codes are generated in the preset folder. It may take some time to complete the process. Next, we just need to open the generated files and copy them in our main CCS code.

How to create a new CCS project and use Grace is well documented in this video: https://www.youtube.com/watch?v=QCYMbsKwRfY.

UniFlash

Most of the times during development, a separate standalone programmer software is not a compulsory necessity as CCS IDE provides an inbuilt programmer/debugger interface. However, at times long after final application development, it becomes completely unnecessary to reopen CCS just to load a firmware to a new micro. UniFlash comes in aid at that time.

Run Uniflash by clicking its icon.

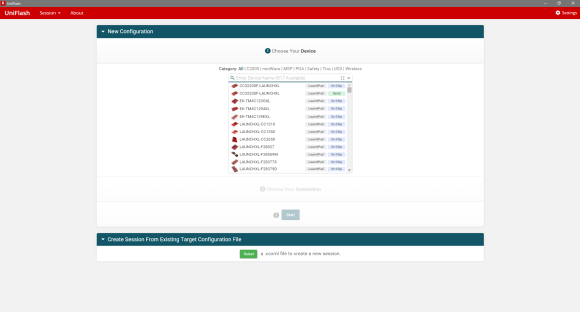

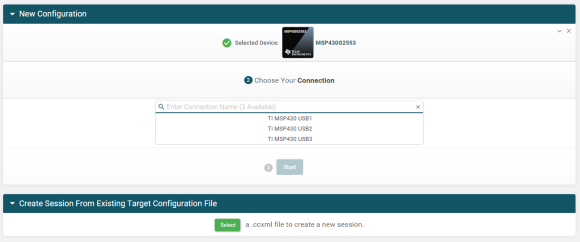

The following window appears:

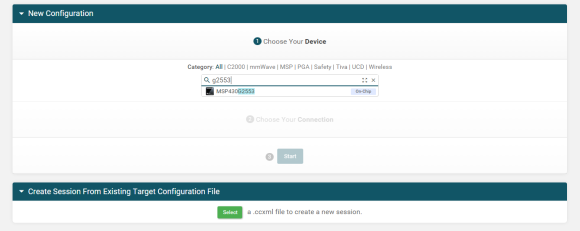

From here we need to select either target board or target microcontroller. No need to type the whole part number of a micro, just few digits/letters are enough to find the correct micro:

Similarly, we need to setup connection to target too. USB1 – the first option is what we need to select.

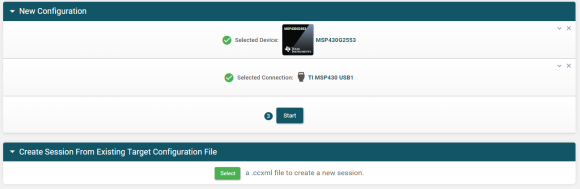

Now we are ready to begin firmware upload. Click the Start button.

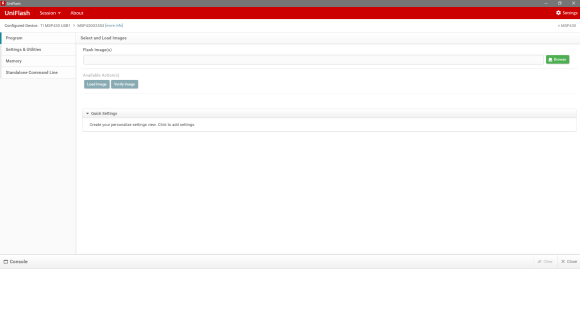

Browse the firmware you wish to upload.

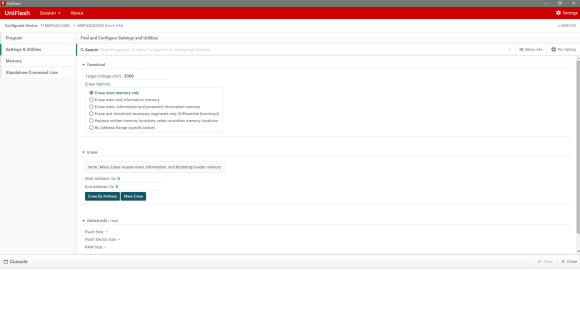

You can optionally set some more parameters for the target as shown:

To flash new firmware, just hit the Load Image button.

Watch this video for details: https://www.youtube.com/watch?v=4uwQSSX-HrM.

Strategies and Tactics

Before we begin exploring MSP430 micros, I would like to discuss certain things though they may look like advanced stuffs for the moment.

Generating HEX Output Files

By default, CCS doesn’t generate any hex formatted output file. Everyone working in the embedded system sector is familiar with it. Hex outputs are useful for Proteus VSM simulations and loading code to a new MSP430 micro using an external programmer like UniFlash. Thus, it is essential if not imperative to unlock hex utility.

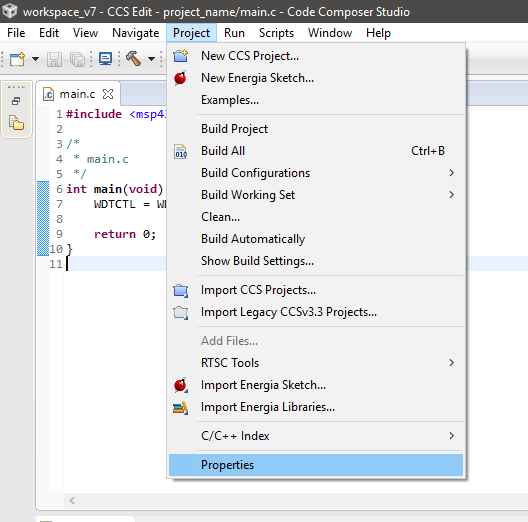

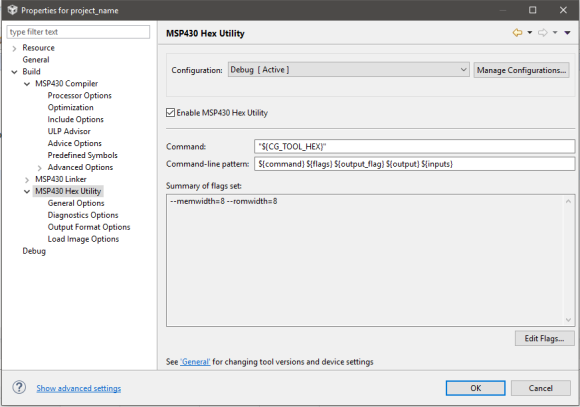

First go to Project >> Properties.

Navigate to find MSP430 Hex Utility and then enable it as shown below.

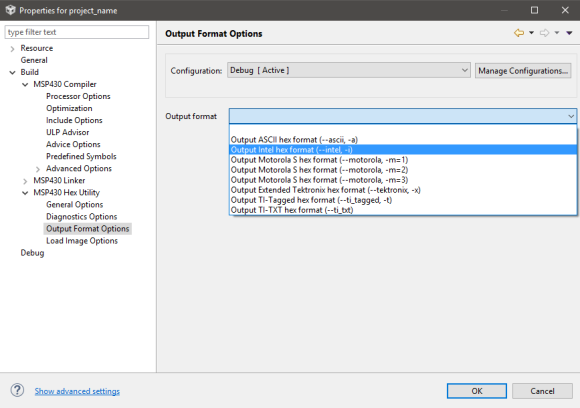

Finally select hex output format as shown:

Select Intel hex format as it is the one widely used.

Having set as shown, from now on, whenever you build your current project, you’ll get an output .hex file in the project’s debug/release folder depending on your project type selection.

Building New Libraries

Building new libraries is simple. All we need to do is to follow a few set of rules:

- For each module, there should be a separate header file and source file.

- Header file should contain definitions, variables, constants and function prototypes only.

- Header files should begin with the inclusion of MSP430 header file.

- Source files should include their respective header files and addition header files (if any).

- Source files should contain actual function codes only.

- Be aware of reserved keywords and constants.

- Global variables with same names should never be declared more than once.

- Empty functions and functions without prototypes must be avoided.

- Functions should have small and meaningful names.

- Be careful about case-senstivity, function type assignment and argument type of functions.

- Hierarchical order of library inclusion must be followed.

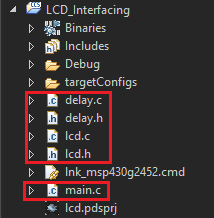

Adding Custom Library Files

Adding own developed libraries to a project is key requirement for any software developer. This is because no compiler includes libraries for all hardware. We must realize a compiler as a tool only. The rest is how we use it and what we do with it. As for example, CCS comes with _delay_cycles instead of more commonly preferred delay_ms or delay_us functions. We will, thus, need software delay library. We need to code it and include it in our projects.

Custom libraries can be included in two ways. The easiest way is to add the include and source files in your projects root location, i.e. its folder. No additional job is needed because the root contains the main.c source file and its location is automatically included when you start a project.

However, the aforementioned method becomes clumsy and unprofessional when there are too many custom library files in a large project and if you care for some neatness. The other method needs some additional tasks to be done before we can use our library files.

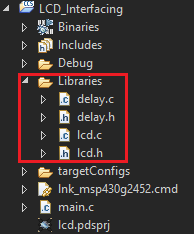

First make a folder in your project directory and give it a name. For example, I named this folder Libraries in my examples.

Next add the desired library source and header files in this folder.

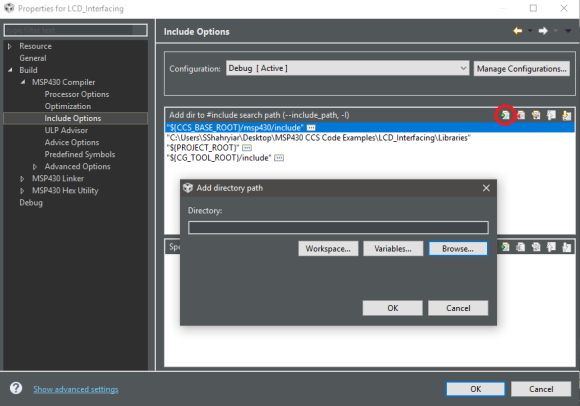

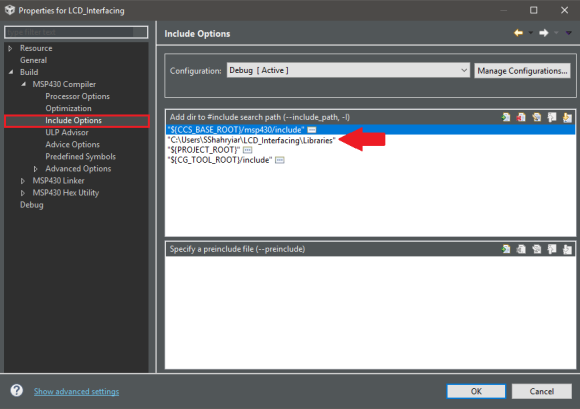

At this stage, we still cannot use these libraries because the compiler does not know their path(s) and so we need to inform the compiler about their location. We need to go to Project >> Properties first and then navigate to Include Options menu under Build >> MSP430 Compiler menu as shown:

Right after clicking the circled icon as shown above, we will be asked for folder location. It is just a simple browsing to the library folder location.

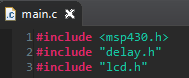

To use the libraries we added, we now just need to add some #include statements in our main.c file.

Be careful about the hierarchical order of library files because they may be interdependent. For example, as shown above, the LCD library has dependency on software delay library and so the delay library is added or called before the LCD library.

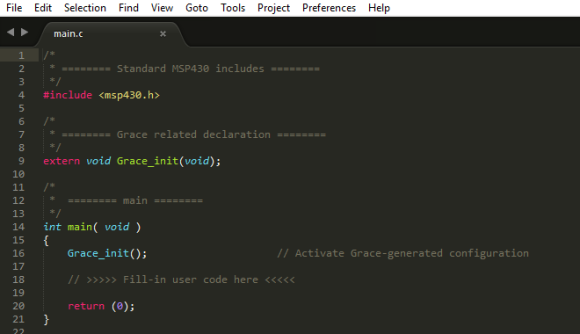

Using GRACE Simply but Effectively

GRACE should be used for quick setups. Who would like to waste time fixing register values when we have such a useful tool at our side. We will need a code viewer/editor like Sublime Text for viewing codes generated by GRACE. I like Sublime Text for its way of highlighting keywords and important stuffs with different colours. This helps in building quick situational awareness. A dark IDE is also good for night-time coding and less stressful for eyes.

Previously I showed how to use GRACE to generate configuration codes. GRACE generates individual source files for each hardware used. In this way, it doesn’t create too much mess. We will open each of these files with Sublime Text and copy only the needed init functions in our main source code. GRACE also generates other stuffs but that are like mere junks to us and so we will just ignore them.

My code examples will give you an idea of what to copy. Keep in mind to stop the watchdog timer in the beginning of your code or it may reset your micro before entering actual application.

Optional Customizations

Explore the IDE Preferences for customizing CCS IDE according to your wishes. For instance, unlike the default white theme, I like a full black IDE interface like the one in Sublime Text. This is really effective when you work at night and in low light conditions. Just like Sublime Text key words are highlighted and it is easy to navigate in such an environment.

In a busy world, we often forget to update software in regular schedules and therefore miss important changes and bug fixes. Automatic updates come in aid in such case. I configured my CCS in such a way that it auto updates and notifies me about new software versions. I also added some tools from CCS/TI App Store like the GCC compiler.

Other customizations include MSP430Ware and EnergyTrace Technology debugger. EnergyTrace Technology allows us to compute energy consumptions. It helps in estimating battery requirements (if any).

I recommend readers to explore CCS IDE properties for more custom settings.

Advanced Concepts

Most of the times during code compilation you’ll notice that the compiler not only compiled your code but has also given you some optional advices. These advices aid in code optimizations and hint ways to enhance overall performance. For instance, it is better to use switch-case statements instead of if-else statements when dealing with fixed-discrete conditions. Try to follow the advices whenever possible. Same goes for compiler warnings. You must address the warnings for flawless coding.

In the internet, we can find lot of documents on C code optimization and good C language practices. Here is one such document from Atmel: http://www.atmel.com/images/doc8453.pdf. Although it was written for Atmel AVR microcontrollers but the document applies for all microcontrollers and C compilers. Similarly, Microchip has documents named Tips ‘n Tricks. Visit and search Microchip’s site for these documents These tricks and tips help in designs significantly. Try to follow these to achieve best utilization of your micro’s assets. TI’s application notes are also equally helpful literatures. Personally, I recommend studying the app notes, and other documents of other micro families too. This will help advance in developing new concepts, strategies and techniques.

Additionally, I would like to point out some issues and techniques when using CCS. Here are followings:

- Be careful about case sensitivity. Also, be careful about compiler’s reserved keywords and constants.

- Although not mandatory, it is, however, a good practice not to keep empty argument field in any function. Argumentless functions should have void argument instead of empty spaces.

- Flags are important event markers and so wherever they are present and needed you must use and check them unless automatically cleared. For instance, it necessary to clear timer flags upon exiting timer interrupts.

- Try to avoid polling methods. Try to use interrupt-based ones but make sure that there is no interrupt-within-interrupt case or otherwise your code may behave erratically. Best is to attach interrupts for important tasks like timing-related jobs, ADC conversions and communications. It is up to your design requirements and choices.

- Where fast processing is required, try to mix assembly with your C-code if you can or temporarily speed up your micro by increasing its oscillator speed or switching to a faster clock source. Checkout the assembly examples from TI’s Resource Explorer and MSP430Ware. Also try to study and learn about advanced C concepts like pointer, structures, functions, etc.

- Avoid empty loops and blank conditional statements.

- When you hover mouse cursor over a function, a small window appears. This window shows the internal coding of that function and relieve you from opening a new tab for it.

- CTRL + Space or code assist is a great helper. Likewise, CCS has some auto complete features.

- If you are using multiple computers during your project’s development stage, make sure that your custom library locations and workspace paths are properly added.

- Try to follow compiler advices and optimizations. Study the MSP430 header files if you can.

- You can straight include the header file of your target MCU like as shown below if code cross compatibility among different MCUs of the same group like MSP430x2xx is not needed:

#include <msp430g2553.h>instead of:

#include <msp430.h>The latter is universal for all MSP430 micros and should be used unless otherwise.

- Bitwise and logic operations are useful. Not only they are fast, they just deal with the designated bits only. Although the MSP430 header files have efficient support for such operations, it is still better to know them. Shown below are some such common operations:

#define bit_set(reg, bit_val) reg |= (1 << bit_val) //For setting a bit of a register

#define bit_clr(reg, bit_val) reg &= (~(1 << bit_val)) //For clearing a bit of a register

#define bit_tgl(reg, bit_val) reg ^= (1 << bit_val) //For toggling a bit of a register

#define get_bit(reg, bit_val) (reg & (1 << bit_val)) //For extracting the bit state of a register

#define get_reg(reg, msk) (reg & msk) //For extracting masked bits of a register

Basic Clock System Plus (BCS+)

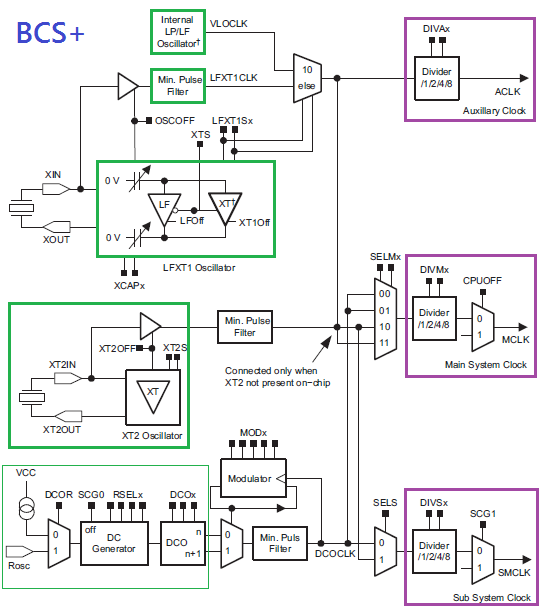

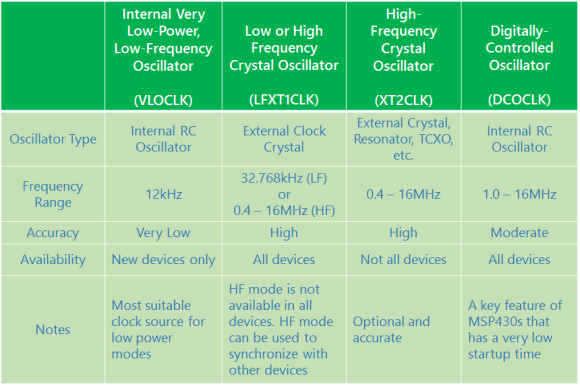

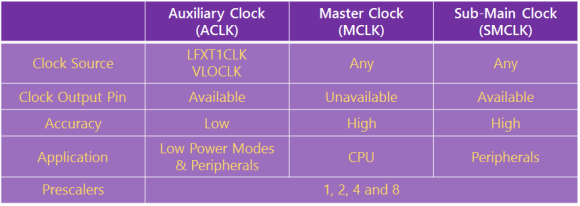

In all microcontrollers, power consumption and operating speed are interdependent and it is needed to balance these well to maximize overall performance while conserving energy. MSP430s are crafted with ultra-low power consumption feature in mind while not compromising performance. For this reason, MSP430s are equipped with a number of clock sources that vary in speed, accuracy and area of use. They also have clock dividers at various points apart from peripherals prescalers. This combination leads to a highly flexible clock system called Basic Clock System Plus (BCS+).

The block diagram for MSP420x2xx BCS+ module shown above highlights important components. It looks very sophisticated but if we divide it into important sections then it becomes simple to understand. Highlighted in green are clock sources and highlighted in purple are various clock signals that can be used for peripherals and the CPU. Now let’s check BCS+ in short.

After having a sneak-a-peek of the MSP430’s clock system, we have to know some basic rules of using the BCS+ module of MSP430G2xx devices:

- XT2CLK and LFXT1CLK high frequency mode are both unavailable. We can’t use them.

- DCOCLK is the most reliable clock source and should be used for both MCLK and SMCLK.

- DCOCLK is dependent on VDD and so set VDD in GRACE before trying to setup BCS+.

- Pre-calibrated DCOCLK values should be used as they offer good tolerance figures.

- It is not wise to use custom DCOCLK values as accuracy issues surface.

- If LFXT1CLK is used and needs precise timings, use a good clock crystal/TCXO/clock source.

- Use proper capacitance value for LFXT1CLK when an external crystal is used.

- Unused clock sources should be disabled to reduce power consumption.

- Pins that connect with external clock sources should be set as inputs if they are not used.

- Add a system start up delay of about 10 – 100ms to allow stabilization of clock sources.

- Clock outputs are available only in certain pins. If used, they are needed to be set accordingly.

- Use oscillator fault interrupt if needed. This becomes extremely necessary to ensure fail-safe clock operation when external clock sources are used alongside internal clock sources.

- For time sensitive hardware like timers, try to use a reliable clock source.

- Check for warnings in GRACE.

Code Example

#include <msp430.h>

void BCSplus_graceInit(void);

void GPIO_graceInit(void);

void WDTplus_graceInit(void);

void System_graceInit(void);

void main(void)

{

/* Stop watchdog timer from timing out during initial start-up. */

WDTCTL = WDTPW | WDTHOLD;

/* initialize Config for the MSP430 GPIO */

GPIO_graceInit();

/* initialize Config for the MSP430 2xx family clock systems (BCS) */

BCSplus_graceInit();

/* initialize Config for the MSP430 System Registers */

System_graceInit();

/* initialize Config for the MSP430 WDT+ */

WDTplus_graceInit();

while(1)

{

P1OUT ^= BIT6;

_delay_cycles(1);

};

}

void BCSplus_graceInit(void)

{

/* USER CODE START (section: BCSplus_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: BCSplus_graceInit_prologue) */

/*

* Basic Clock System Control 2

*

* SELM_0 -- DCOCLK

* DIVM_1 -- Divide by 2

* SELS -- XT2CLK when XT2 oscillator present. LFXT1CLK or VLOCLK when XT2 oscillator not present

* DIVS_3 -- Divide by 8

* ~DCOR -- DCO uses internal resistor

*

* Note: ~DCOR indicates that DCOR has value zero

*/

BCSCTL2 = SELM_0 | DIVM_1 | SELS | DIVS_3;

if (CALBC1_1MHZ != 0xFF) {

/* Follow recommended flow. First, clear all DCOx and MODx bits. Then

* apply new RSELx values. Finally, apply new DCOx and MODx bit values.

*/

DCOCTL = 0x00;

BCSCTL1 = CALBC1_1MHZ; /* Set DCO to 1MHz */

DCOCTL = CALDCO_1MHZ;

}

/*

* Basic Clock System Control 1

*

* XT2OFF -- Disable XT2CLK

* ~XTS -- Low Frequency

* DIVA_0 -- Divide by 1

*

* Note: ~XTS indicates that XTS has value zero

*/

BCSCTL1 |= XT2OFF | DIVA_0;

/*

* Basic Clock System Control 3

*

* XT2S_0 -- 0.4 - 1 MHz

* LFXT1S_2 -- If XTS = 0, XT1 = VLOCLK ; If XTS = 1, XT1 = 3 - 16-MHz crystal or resonator

* XCAP_1 -- ~6 pF

*/

BCSCTL3 = XT2S_0 | LFXT1S_2 | XCAP_1;

/* USER CODE START (section: BCSplus_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: BCSplus_graceInit_epilogue) */

}

void GPIO_graceInit(void)

{

/* USER CODE START (section: GPIO_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: GPIO_graceInit_prologue) */

/* Port 1 Output Register */

P1OUT = 0;

/* Port 1 Port Select Register */

P1SEL = BIT0 | BIT4;

/* Port 1 Direction Register */

P1DIR = BIT0 | BIT4 | BIT6;

/* Port 1 Interrupt Edge Select Register */

P1IES = 0;

/* Port 1 Interrupt Flag Register */

P1IFG = 0;

/* Port 2 Output Register */

P2OUT = 0;

/* Port 2 Direction Register */

P2DIR = 0;

/* Port 2 Interrupt Edge Select Register */

P2IES = 0;

/* Port 2 Interrupt Flag Register */

P2IFG = 0;

/* Port 3 Output Register */

P3OUT = 0;

/* Port 3 Direction Register */

P3DIR = 0;

/* USER CODE START (section: GPIO_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: GPIO_graceInit_epilogue) */

}

void WDTplus_graceInit(void)

{

/* USER CODE START (section: RTC_B_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: RTC_B_graceInit_prologue) */

/*

* WDTCTL, Watchdog Timer+ Register

*

* WDTPW -- Watchdog password

* WDTHOLD -- Watchdog timer+ is stopped

* ~WDTNMIES -- NMI on rising edge

* ~WDTNMI -- Reset function

* ~WDTTMSEL -- Watchdog mode

* ~WDTCNTCL -- No action

* ~WDTSSEL -- SMCLK

* ~WDTIS0 -- Watchdog clock source bit0 disabled

* ~WDTIS1 -- Watchdog clock source bit1 disabled

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

WDTCTL = WDTPW | WDTHOLD;

/* USER CODE START (section: RTC_B_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: RTC_B_graceInit_epilogue) */

}

void System_graceInit(void)

{

/* USER CODE START (section: System_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: System_graceInit_prologue) */

/* Clear oscillator fault flag with software delay */

do

{

// Clear OSC fault flag

IFG1 &= ~OFIFG;

// 50us delay

__delay_cycles(25);

} while (IFG1 & OFIFG);

/*

* SR, Status Register

*

* ~SCG1 -- Disable System clock generator 1

* ~SCG0 -- Disable System clock generator 0

* ~OSCOFF -- Oscillator On

* ~CPUOFF -- CPU On

* GIE -- General interrupt enable

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

__bis_SR_register(GIE);

/* USER CODE START (section: System_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: System_graceInit_epilogue) */

}

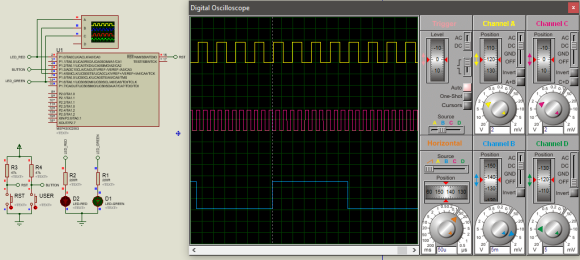

Simulation

Explanation

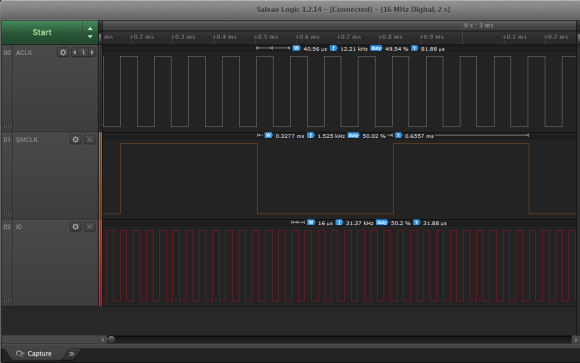

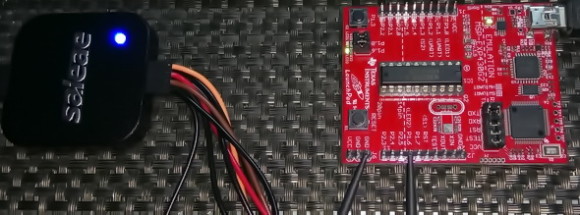

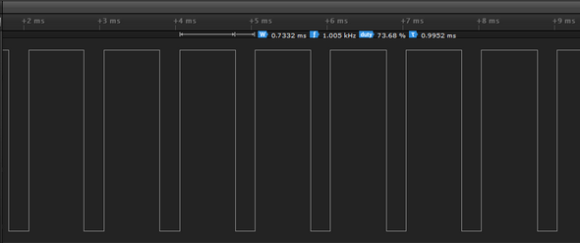

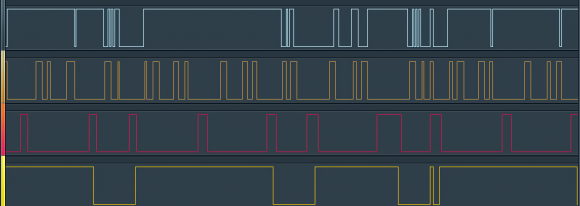

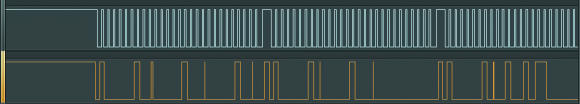

The demo example here is primarily used to extract SMCLK and ACLK signals. Here we just verified if these signals are as they are supposed to be. Using GRACE, we set MCLK 500 kHz, SMCLK 1500 Hz and ACLK 12 kHz. Clock outputs are obtained from respective pins as shown in the snap. The only thing additional here (not shown) is the P1.6 digital I/O. In the code, this I/O is toggled every one CPU cycle. It is not an indicator of CPU clock speed but just a test of I/O toggling speed for. MCLK has no output associated with it and so we can’t see its signal.

One major thing to note is the power supply voltage level. This is so because DCOCLK is dependent on VDD level. For low VDD voltages, high frequency oscillation generation is not possible. We have to remember that MSP430s are energy efficient devices and so there is always a trade-off between operating frequency and operating power consumption.

Another odd but important thing you may notice is the fact that the VDD value in MSP430 Launchpads is 3.6V instead of the more commonly used 3.3V. This is the maximum recommended VDD value although MSP430s can tolerate voltages up to 4.0V.

Oscillators may show deviations in frequency due to changes in ambient temperature conditions. This in turn may affect communication and timing-related tasks.

Demo

Demo video: https://www.youtube.com/watch?v=gHDibVxfegU.

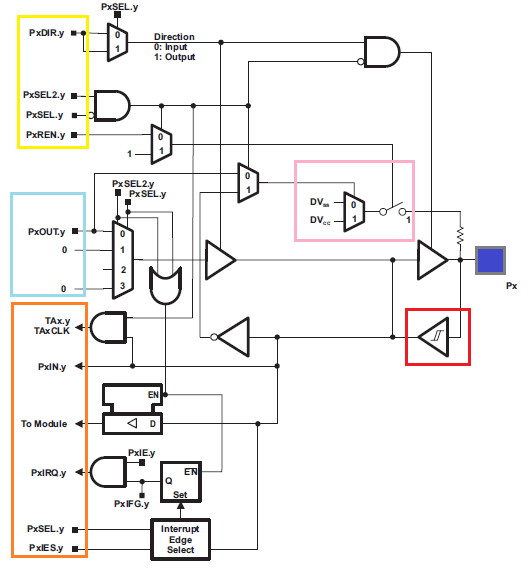

Digital I/Os (DIO)

MSP430s, just like any micro, have digital I/Os for general-purpose input-output operations. The resources and features of MSP430 digital I/Os are very rich and more or less comparable to a typical ARM microcontroller. All I/O can be independently programmed. Many I/Os have external interrupt feature. Another cool feature is the availability of both internal pull-up and pull-down resistors for all I/Os and they can be individually and independently set. Additionally, many I/Os have alternate roles for communication buses, clock, etc. However, the digital I/Os are not 5V tolerant and we must be careful interfacing external devices with our MSP430 chips. I strongly recommend using some form of logic-level conversion circuitry in such cases.

Typically, there are four major components in a digital I/O as highlighted in the block diagram above. The yellow region is responsible for setting I/O properties, the light blue area is dedicated for output functionalities, the orange area for inputs and external interrupts, the pink zone for internal pull resistors and finally the red area signifying the presence of a Schmitt trigger input stage which is very useful for noisy environments.

Code Example

#include <msp430g2452.h>

void GPIO_graceInit(void);

void BCSplus_graceInit(void);

void WDTplus_graceInit(void);

void System_graceInit(void);

void main(void)

{

/* Stop watchdog timer from timing out during initial start-up. */

WDTCTL = WDTPW | WDTHOLD;

/* initialize Config for the MSP430 GPIO */

GPIO_graceInit();

/* initialize Config for the MSP430 2xx family clock systems (BCS) */

BCSplus_graceInit();

/* initialize Config for the MSP430 System Registers */

System_graceInit();

/* initialize Config for the MSP430 WDT+ */

WDTplus_graceInit();

for(;;)

{

if((P1IN & BIT3) == !BIT3)

{

P1OUT |= BIT0;

_delay_cycles(40000);

P1OUT &= ~BIT0;

}

P1OUT ^= BIT6;

_delay_cycles(30000);

}

}

void BCSplus_graceInit(void)

{

/* USER CODE START (section: BCSplus_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: BCSplus_graceInit_prologue) */

/*

* Basic Clock System Control 2

*

* SELM_0 -- DCOCLK

* DIVM_0 -- Divide by 1

* ~SELS -- DCOCLK

* DIVS_0 -- Divide by 1

* ~DCOR -- DCO uses internal resistor

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

BCSCTL2 = SELM_0 | DIVM_0 | DIVS_0;

if (CALBC1_1MHZ != 0xFF) {

/* Follow recommended flow. First, clear all DCOx and MODx bits. Then

* apply new RSELx values. Finally, apply new DCOx and MODx bit values.

*/

DCOCTL = 0x00;

BCSCTL1 = CALBC1_1MHZ; /* Set DCO to 1MHz */

DCOCTL = CALDCO_1MHZ;

}

/*

* Basic Clock System Control 1

*

* XT2OFF -- Disable XT2CLK

* ~XTS -- Low Frequency

* DIVA_0 -- Divide by 1

*

* Note: ~XTS indicates that XTS has value zero

*/

BCSCTL1 |= XT2OFF | DIVA_0;

/*

* Basic Clock System Control 3

*

* XT2S_0 -- 0.4 - 1 MHz

* LFXT1S_2 -- If XTS = 0, XT1 = VLOCLK ; If XTS = 1, XT1 = 3 - 16-MHz crystal or resonator

* XCAP_1 -- ~6 pF

*/

BCSCTL3 = XT2S_0 | LFXT1S_2 | XCAP_1;

/* USER CODE START (section: BCSplus_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: BCSplus_graceInit_epilogue) */

}

void GPIO_graceInit(void)

{

/* USER CODE START (section: GPIO_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: GPIO_graceInit_prologue) */

/* Port 1 Output Register */

P1OUT = BIT3;

/* Port 1 Direction Register */

P1DIR = BIT0 | BIT6;

/* Port 1 Resistor Enable Register */

P1REN = BIT3;

/* Port 1 Interrupt Edge Select Register */

P1IES = 0;

/* Port 1 Interrupt Flag Register */

P1IFG = 0;

/* Port 2 Output Register */

P2OUT = 0;

/* Port 2 Direction Register */

P2DIR = 0;

/* Port 2 Interrupt Edge Select Register */

P2IES = 0;

/* Port 2 Interrupt Flag Register */

P2IFG = 0;

/* USER CODE START (section: GPIO_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: GPIO_graceInit_epilogue) */

}

void System_graceInit(void)

{

/* USER CODE START (section: System_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: System_graceInit_prologue) */

/* Clear oscillator fault flag with software delay */

do

{

// Clear OSC fault flag

IFG1 &= ~OFIFG;

// 50us delay

__delay_cycles(50);

} while (IFG1 & OFIFG);

/*

* SR, Status Register

*

* ~SCG1 -- Disable System clock generator 1

* ~SCG0 -- Disable System clock generator 0

* ~OSCOFF -- Oscillator On

* ~CPUOFF -- CPU On

* GIE -- General interrupt enable

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

__bis_SR_register(GIE);

/* USER CODE START (section: System_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: System_graceInit_epilogue) */

}

void WDTplus_graceInit(void)

{

/* USER CODE START (section: RTC_B_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: RTC_B_graceInit_prologue) */

/*

* WDTCTL, Watchdog Timer+ Register

*

* WDTPW -- Watchdog password

* WDTHOLD -- Watchdog timer+ is stopped

* ~WDTNMIES -- NMI on rising edge

* ~WDTNMI -- Reset function

* ~WDTTMSEL -- Watchdog mode

* ~WDTCNTCL -- No action

* ~WDTSSEL -- SMCLK

* ~WDTIS0 -- Watchdog clock source bit0 disabled

* ~WDTIS1 -- Watchdog clock source bit1 disabled

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

WDTCTL = WDTPW | WDTHOLD;

/* USER CODE START (section: RTC_B_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: RTC_B_graceInit_epilogue) */

}

Simulation

Explanation

The most classical “Hello World” demo for digital I/Os is blinking a LED. Here I demonstrated the same but with some minor differences. Here Launchpad board’s user button and LEDs are used. LED connected to P1.6 blinks continuously while P1.0 LED blinks only when the user button is pressed, slowing down P1.6 LED’s blink rate. Note _delay_cycles were used to create software delays.

At this stage I must point out, some basic rules that we must follow when we use digital I/Os of MSP430s:

- Unused I/Os should be declared as inputs or they should be externally pulled to VDD/VSS.

- Unused digital I/Os can be left unconnected and floating although it is not wise to do so.

- The same applies for oscillator pins. By default, GRACE treats them as oscillator pins.

- I/Os are not 5V tolerant. Some sort of mechanism must be applied when using 5V devices.

- Most I/Os have more than one function and so be aware of conflicts.

- When driving large loads with I/O, use external components like BJTs, FETs, drivers, etc.

- When using GRACE, be sure of the IC package you are using.

- When external pull resistor is present, do not use the internal ones and vice versa.

- Explore your device’s datasheet for I/O features and limits although most are common.

Demo

Demo video: https://www.youtube.com/watch?v=fWlNiEZk4iM.

External Interrupts (EXTI)

External interrupt is an extended feature of digital I/Os in input mode. External interrupts make a micro to respond instantly to changes done on it digital input pin(s) by an external event(s)/trigger(s), skipping other tasks. Such interrupts are useful in a wide variety of applications. In case of low power energy efficient micros like the MSP430s, interrupts as such can be used to bring a micro out of sleep mode. In other words, an external interrupt acts like a wakeup call. For example, it is extremely important to conserve very limited battery energy in a TV remote controller while at the same time it is also necessary to keep it completely responsive to button presses. Thus, we need to put its host micro in sleep mode when we are not using it and make it respond to button presses immediately when any button is pressed. A MSP430 micro in sleep/idle mode consumes literally no energy at all and that is why they are the best micros for battery-backed low power applications.

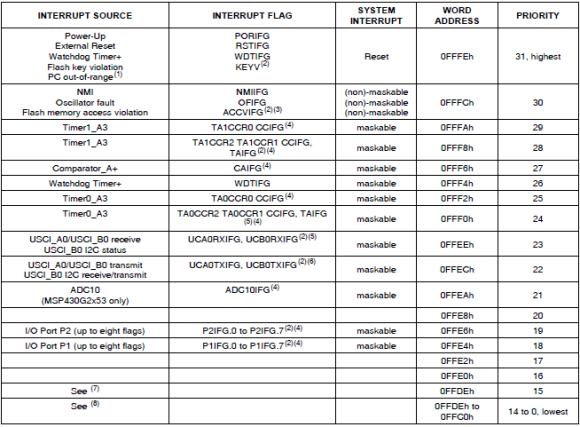

Fortunately for us, most MSP430G2xx digital I/Os have external interrupt handling capability – a much desired feature. Shown above is the interrupt map for MSP430G2553. Note external interrupts are maskable interrupts and have low priority compares to other interrupts. We must consider this fact when coding a multi-interrupt-based application.

Code Example

#include <MSP430G2452.h>

unsigned char state = 0x00;

void BCSplus_graceInit(void);

void GPIO_graceInit(void);

void System_graceInit(void);

void WDTplus_graceInit(void);

#pragma vector=PORT1_VECTOR

__interrupt void PORT1_ISR_HOOK(void)

{

state = ~state;

P1OUT ^= BIT0;

P1IFG = 0x00;

}

void main(void)

{

/* Stop watchdog timer from timing out during initial start-up. */

WDTCTL = WDTPW | WDTHOLD;

/* initialize Config for the MSP430 GPIO */

GPIO_graceInit();

/* initialize Config for the MSP430 2xx family clock systems (BCS) */

BCSplus_graceInit();

/* initialize Config for the MSP430 System Registers */

System_graceInit();

/* initialize Config for the MSP430 WDT+ */

WDTplus_graceInit();

do

{

P1OUT ^= BIT6;

if(state)

{

_delay_cycles(60000);

}

else

{

_delay_cycles(30000);

}

}while(1);

}

void BCSplus_graceInit(void)

{

/* USER CODE START (section: BCSplus_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: BCSplus_graceInit_prologue) */

/*

* Basic Clock System Control 2

*

* SELM_0 -- DCOCLK

* DIVM_0 -- Divide by 1

* ~SELS -- DCOCLK

* DIVS_0 -- Divide by 1

* ~DCOR -- DCO uses internal resistor

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

BCSCTL2 = SELM_0 | DIVM_0 | DIVS_0;

if (CALBC1_1MHZ != 0xFF) {

/* Follow recommended flow. First, clear all DCOx and MODx bits. Then

* apply new RSELx values. Finally, apply new DCOx and MODx bit values.

*/

DCOCTL = 0x00;

BCSCTL1 = CALBC1_1MHZ; /* Set DCO to 1MHz */

DCOCTL = CALDCO_1MHZ;

}

/*

* Basic Clock System Control 1

*

* XT2OFF -- Disable XT2CLK

* ~XTS -- Low Frequency

* DIVA_0 -- Divide by 1

*

* Note: ~XTS indicates that XTS has value zero

*/

BCSCTL1 |= XT2OFF | DIVA_0;

/*

* Basic Clock System Control 3

*

* XT2S_0 -- 0.4 - 1 MHz

* LFXT1S_2 -- If XTS = 0, XT1 = VLOCLK ; If XTS = 1, XT1 = 3 - 16-MHz crystal or resonator

* XCAP_1 -- ~6 pF

*/

BCSCTL3 = XT2S_0 | LFXT1S_2 | XCAP_1;

/* USER CODE START (section: BCSplus_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: BCSplus_graceInit_epilogue) */

}

void GPIO_graceInit(void)

{

/* USER CODE START (section: GPIO_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: GPIO_graceInit_prologue) */

/* Port 1 Output Register */

P1OUT = 0;

/* Port 1 Direction Register */

P1DIR = BIT0 | BIT6;

/* Port 1 Interrupt Edge Select Register */

P1IES = BIT3;

/* Port 1 Interrupt Flag Register */

P1IFG = 0;

/* Port 1 Interrupt Enable Register */

P1IE = BIT3;

/* Port 2 Output Register */

P2OUT = 0;

/* Port 2 Port Select Register */

P2SEL &= ~(BIT6 | BIT7);

/* Port 2 Direction Register */

P2DIR = 0;

/* Port 2 Interrupt Edge Select Register */

P2IES = 0;

/* Port 2 Interrupt Flag Register */

P2IFG = 0;

/* USER CODE START (section: GPIO_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: GPIO_graceInit_epilogue) */

}

void System_graceInit(void)

{

/* USER CODE START (section: System_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: System_graceInit_prologue) */

/* Clear oscillator fault flag with software delay */

do

{

// Clear OSC fault flag

IFG1 &= ~OFIFG;

// 50us delay

__delay_cycles(50);

} while (IFG1 & OFIFG);

/*

* SR, Status Register

*

* ~SCG1 -- Disable System clock generator 1

* ~SCG0 -- Disable System clock generator 0

* ~OSCOFF -- Oscillator On

* ~CPUOFF -- CPU On

* GIE -- General interrupt enable

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

__bis_SR_register(GIE);

/* USER CODE START (section: System_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: System_graceInit_epilogue) */

}

void WDTplus_graceInit(void)

{

/* USER CODE START (section: RTC_B_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: RTC_B_graceInit_prologue) */

/*

* WDTCTL, Watchdog Timer+ Register

*

* WDTPW -- Watchdog password

* WDTHOLD -- Watchdog timer+ is stopped

* ~WDTNMIES -- NMI on rising edge

* ~WDTNMI -- Reset function

* ~WDTTMSEL -- Watchdog mode

* ~WDTCNTCL -- No action

* ~WDTSSEL -- SMCLK

* ~WDTIS0 -- Watchdog clock source bit0 disabled

* ~WDTIS1 -- Watchdog clock source bit1 disabled

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

WDTCTL = WDTPW | WDTHOLD;

/* USER CODE START (section: RTC_B_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: RTC_B_graceInit_epilogue) */

}

Simulation

Explanation

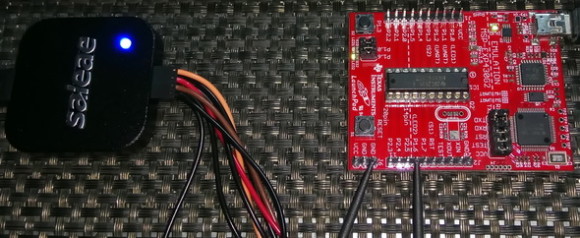

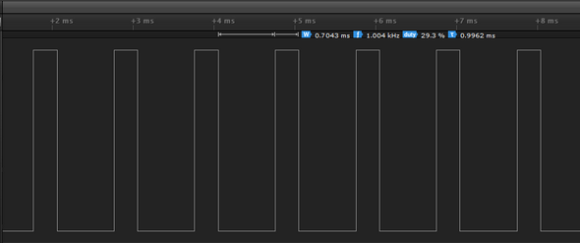

The basic theme and the hardware setup for this demo is same as that of the previous one. The only difference is the Launchpad user button. Rather than using polling method, external interrupt method is used. When P1.3 detects a falling edge, P1.0’s state is altered while P1.6 toggles independently in the main loop, denoting two separate independent processes at work simultaneously. Every external interrupt changes the toggle speed of P1.6 LED.

Demo

Demo video: https://www.youtube.com/watch?v=LlTvj-CSiBE.

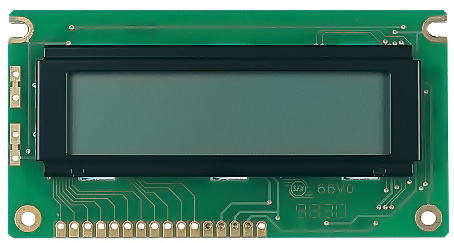

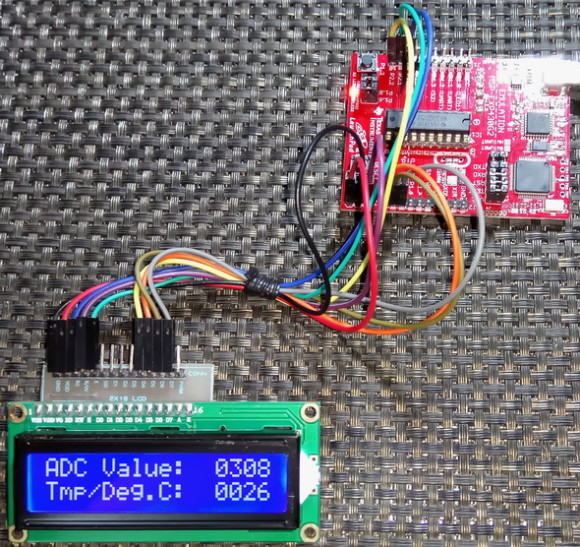

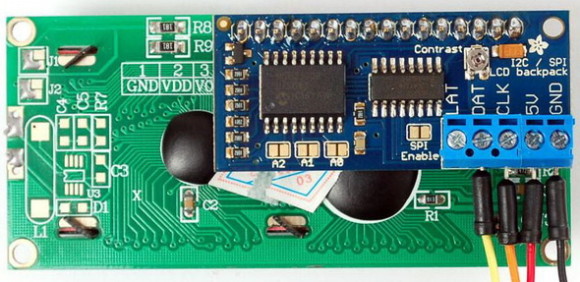

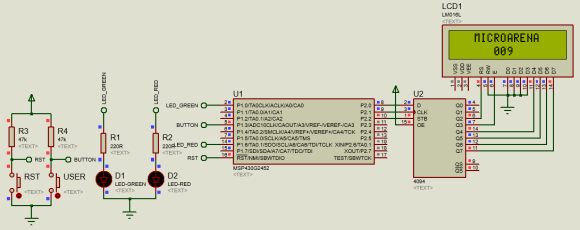

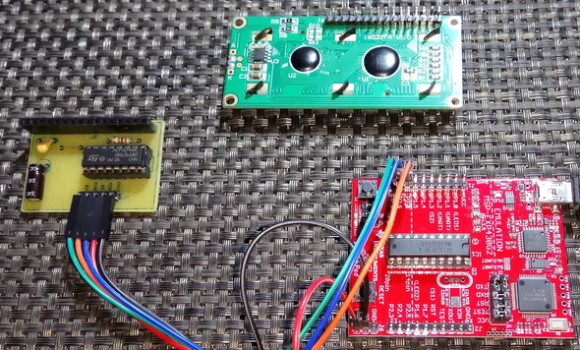

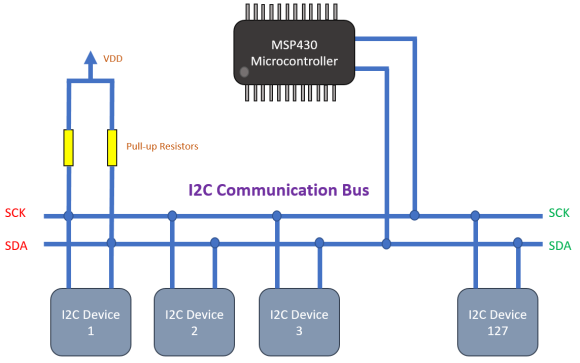

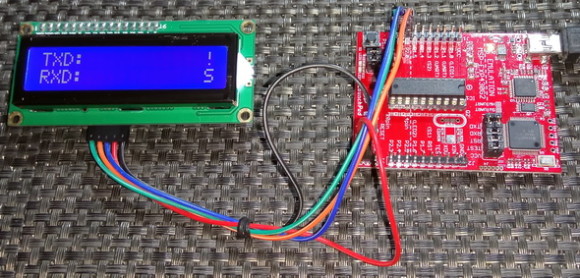

Alphanumeric LCD

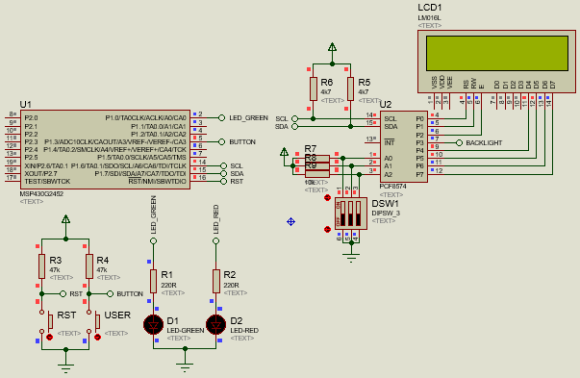

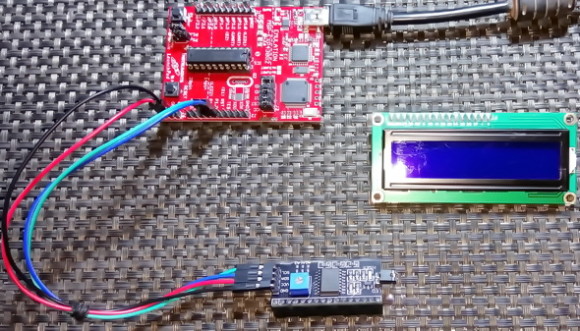

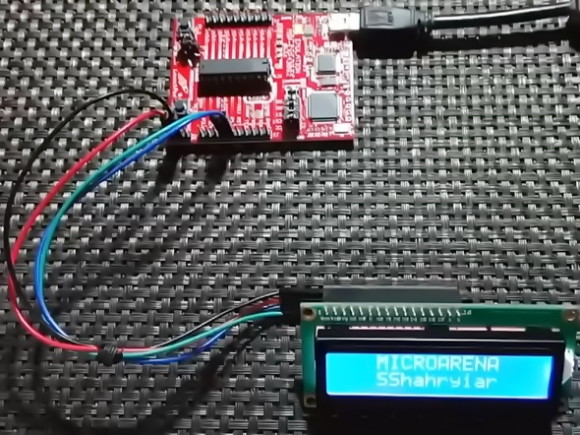

Alphanumeric LCDs are popular for projecting data and information quickly and efficiently. To use them, we do not need any additional hardware feature in a micro. Digital I/Os are what we need to use these displays.

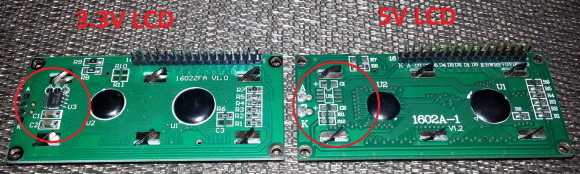

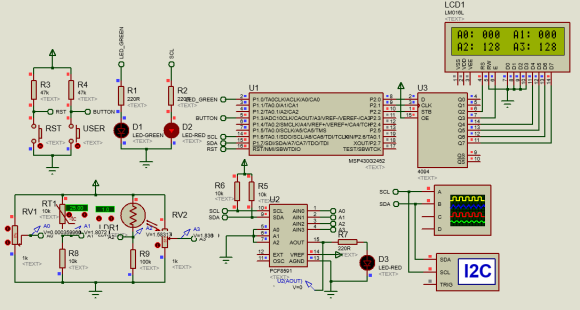

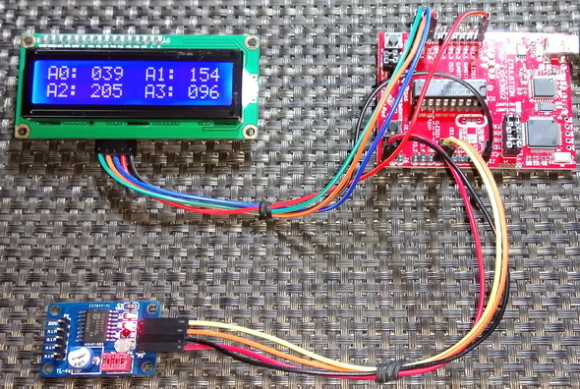

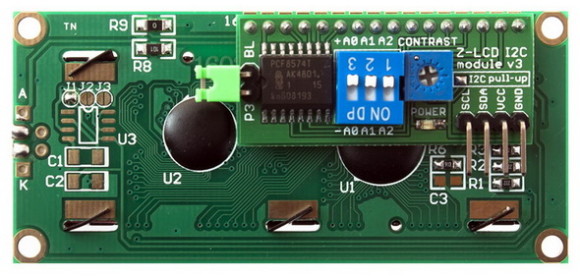

Usually to use these LCDs we need 5V power supply. 3.3V versions of these LCD are rare on the other hand. It is, however, possible to power up 5V version LCDs with 5V supply while using 3.3V logic for communication. In TTL logic, something above 2.8V is just above the minimum allowed logic high voltage. When VDD is less than 3V, it, then, becomes necessary to use logic level conversion circuitry. Here in my demo I used a 3.3V version LCD to keep things simple and tidy. Shown below are LCDs for different voltage levels. Both LCDs look same but if you check the backside of both LCDs you’ll notice a difference. In the 3.3V version LCD, there are some additional components present, notably an 8 pin SMD IC. This is a ICL7660 negative voltage generator IC.

Similarly, alphanumeric LCDs also have operating frequency limit. Usually it is about 250 kHz. Refer to the datasheet of the LCD you are using. If the digital I/Os are faster than this max limit value, it is highly likely that the LCD won’t show any valid data at all or it will show up garbage characters. To counter this issue, either we have to use a low MCU clock frequency or add some delays in our LCD library to slow the processes down.

Software delays are often required to introduce time delays in a code. Such delays will be needed for the LCD library. As discussed before by default, CCS doesn’t provide delay time functions i.e. delay milliseconds (delay_ms) and delay micro-seconds (delay_us). Instead it provides _delay_cycles function for delays. Most of us will not be comfortable with delay cycles function as it doesn’t directly signify the amount of time wasted. Thus, delay time functions are musts. Although software delays are inefficient in terms of coding and performance, they are helpful in debugging stuffs quickly in a rudimentary fashion. A much novel and precise approach of creating time delays is achieved using a timer. In this example, we will need both LCD and delay libraries. I already showed how to incorporate custom libraries in a CCS Project and here I implemented that addition.

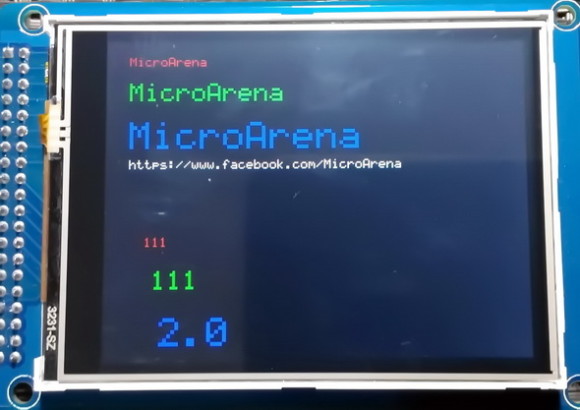

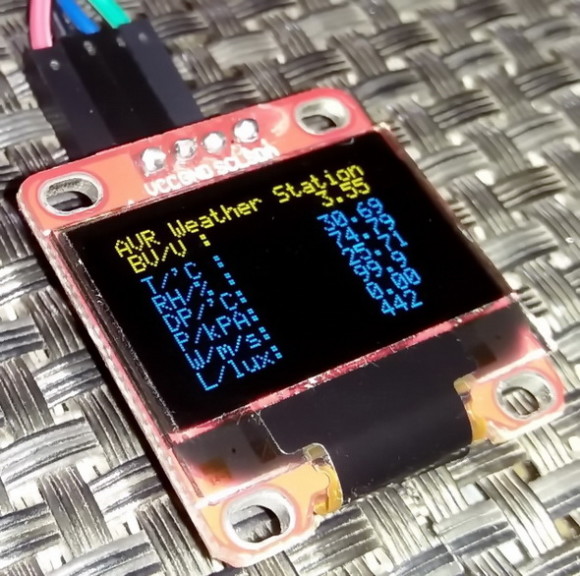

There are other types of displays in the realm of LCDs. These include monochrome graphical LCDs, TFT LCDs, OLED LCDs, etc. However, it is literally impossible to integrate these displays with MSP430G2xx micros. Firstly, this is so due to low memories and secondly due to low pin counts. MSP430G2xx micros are also not as fast as ARM micros. Speed plays a vital role in processing graphics.

Code Example

delay.h

#include <msp430.h>

#define F_CPU 8

void delay_us(unsigned int value);

void delay_ms(unsigned int value);

delay.c

#include "delay.h"

void delay_us(unsigned int value)

{

register unsigned int loops = ((F_CPU * value) >> 2) ;

while(loops)

{

_delay_cycles(1);

loops--;

};

}

void delay_ms(unsigned int value)

{

while(value)

{

delay_us(1000);

value--;

};

}

lcd.h

#include <msp430.h>

#include <delay.h>

#define LCD_PORT P2OUT

#define LCD_RS BIT0

#define LCD_EN BIT1

#define LCD_DB4 BIT2

#define LCD_DB5 BIT3

#define LCD_DB6 BIT4

#define LCD_DB7 BIT5

#define LCD_RS_HIGH LCD_PORT |= LCD_RS

#define LCD_RS_LOW LCD_PORT &= ~LCD_RS

#define LCD_EN_HIGH LCD_PORT |= LCD_EN

#define LCD_EN_LOW LCD_PORT &= ~LCD_EN

#define LCD_DB4_HIGH LCD_PORT |= LCD_DB4

#define LCD_DB4_LOW LCD_PORT &= ~LCD_DB4

#define LCD_DB5_HIGH LCD_PORT |= LCD_DB5

#define LCD_DB5_LOW LCD_PORT &= ~LCD_DB5

#define LCD_DB6_HIGH LCD_PORT |= LCD_DB6

#define LCD_DB6_LOW LCD_PORT &= ~LCD_DB6

#define LCD_DB7_HIGH LCD_PORT |= LCD_DB7

#define LCD_DB7_LOW LCD_PORT &= ~LCD_DB7

#define clear_display 0x01

#define goto_home 0x02

#define cursor_direction_inc (0x04 | 0x02)

#define cursor_direction_dec (0x04 | 0x00)

#define display_shift (0x04 | 0x01)

#define display_no_shift (0x04 | 0x00)

#define display_on (0x08 | 0x04)

#define display_off (0x08 | 0x02)

#define cursor_on (0x08 | 0x02)

#define cursor_off (0x08 | 0x00)

#define blink_on (0x08 | 0x01)

#define blink_off (0x08 | 0x00)

#define _8_pin_interface (0x20 | 0x10)

#define _4_pin_interface (0x20 | 0x00)

#define _2_row_display (0x20 | 0x08)

#define _1_row_display (0x20 | 0x00)

#define _5x10_dots (0x20 | 0x40)

#define _5x7_dots (0x20 | 0x00)

#define DAT 1

#define CMD 0

void LCD_init(void);

void LCD_send(unsigned char value, unsigned char mode);

void LCD_4bit_send(unsigned char lcd_data);

void LCD_putstr(char *lcd_string);

void LCD_putchar(char char_data);

void LCD_clear_home(void);

void LCD_goto(unsigned char x_pos, unsigned char y_pos);

void toggle_EN_pin(void);

void toggle_io(unsigned char lcd_data, unsigned char bit_pos, unsigned char pin_num);

lcd.c

#include "lcd.h"

void LCD_init(void)

{

LCD_PORT |= (LCD_RS | LCD_EN | LCD_DB4 | LCD_DB5 | LCD_DB6 | LCD_DB7);

delay_ms(20);

toggle_EN_pin();

LCD_RS_LOW;

LCD_DB7_LOW;

LCD_DB6_LOW;

LCD_DB5_HIGH;

LCD_DB4_HIGH;

toggle_EN_pin();

LCD_DB7_LOW;

LCD_DB6_LOW;

LCD_DB5_HIGH;

LCD_DB4_HIGH;

toggle_EN_pin();

LCD_DB7_LOW;

LCD_DB6_LOW;

LCD_DB5_HIGH;

LCD_DB4_HIGH;

toggle_EN_pin();

LCD_DB7_LOW;

LCD_DB6_LOW;

LCD_DB5_HIGH;

LCD_DB4_LOW;

toggle_EN_pin();

LCD_send((_4_pin_interface | _2_row_display | _5x7_dots), CMD);

LCD_send((display_on | cursor_off | blink_off), CMD);

LCD_send(clear_display, CMD);

LCD_send((cursor_direction_inc | display_no_shift), CMD);

}

void LCD_send(unsigned char value, unsigned char mode)

{

switch(mode)

{

case DAT:

{

LCD_RS_HIGH;

break;

}

case CMD:

{

LCD_RS_LOW;

break;

}

}

LCD_4bit_send(value);

}

void LCD_4bit_send(unsigned char lcd_data)

{

toggle_io(lcd_data, 7, LCD_DB7);

toggle_io(lcd_data, 6, LCD_DB6);

toggle_io(lcd_data, 5, LCD_DB5);

toggle_io(lcd_data, 4, LCD_DB4);

toggle_EN_pin();

toggle_io(lcd_data, 3, LCD_DB7);

toggle_io(lcd_data, 2, LCD_DB6);

toggle_io(lcd_data, 1, LCD_DB5);

toggle_io(lcd_data, 0, LCD_DB4);

toggle_EN_pin();

}

void LCD_putstr(char *lcd_string)

{

do

{

LCD_send(*lcd_string++, DAT);

}while(*lcd_string != '\0');

}

void LCD_putchar(char char_data)

{

LCD_send(char_data, DAT);

}

void LCD_clear_home(void)

{

LCD_send(clear_display, CMD);

LCD_send(goto_home, CMD);

}

void LCD_goto(unsigned char x_pos, unsigned char y_pos)

{

if(y_pos == 0)

{

LCD_send((0x80 | x_pos), CMD);

}

else

{

LCD_send((0x80 | 0x40 | x_pos), CMD);

}

}

void toggle_EN_pin(void)

{

LCD_EN_HIGH;

delay_ms(2);

LCD_EN_LOW;

delay_ms(2);

}

void toggle_io(unsigned char lcd_data, unsigned char bit_pos, unsigned char pin_num)

{

unsigned char temp = 0x00;

temp = (0x01 & (lcd_data >> bit_pos));

switch(temp)

{

case 0:

{

LCD_PORT &= ~pin_num;

break;

}

default:

{

LCD_PORT |= pin_num;

break;

}

}

}

main.c

#include <msp430.h>

#include "delay.h"

#include "lcd.h"

void GPIO_graceInit(void);

void BCSplus_graceInit(void);

void System_graceInit(void);

void WDTplus_graceInit(void);

void main(void)

{

unsigned char s = 0;

const char txt1[] = {"MICROARENA"};

const char txt2[] = {"SShahryiar"};

const char txt3[] = {"MSP-EXP430G2"};

const char txt4[] = {"Launchpad!"};

/* Stop watchdog timer from timing out during initial start-up. */

WDTCTL = WDTPW | WDTHOLD;

/* initialize Config for the MSP430 GPIO */

GPIO_graceInit();

/* initialize Config for the MSP430 2xx family clock systems (BCS) */

BCSplus_graceInit();

/* initialize Config for the MSP430 System Registers */

System_graceInit();

/* initialize Config for the MSP430 WDT+ */

WDTplus_graceInit();

LCD_init();

LCD_clear_home();

LCD_goto(3, 0);

LCD_putstr(txt1);

LCD_goto(3, 1);

LCD_putstr(txt2);

delay_ms(2600);

LCD_clear_home();

for(s = 0; s < 12; s++)

{

LCD_goto((2 + s), 0);

LCD_putchar(txt3[s]);

delay_ms(90);

}

for(s = 0; s < 10; s++)

{

LCD_goto((3 + s), 1);

LCD_putchar(txt4[s]);

delay_ms(90);

}

while(1)

{

};

}

void GPIO_graceInit(void)

{

/* USER CODE START (section: GPIO_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: GPIO_graceInit_prologue) */

/* Port 1 Output Register */

P1OUT = 0;

/* Port 1 Direction Register */

P1DIR = 0;

/* Port 1 Interrupt Edge Select Register */

P1IES = 0;

/* Port 1 Interrupt Flag Register */

P1IFG = 0;

/* Port 2 Output Register */

P2OUT = 0;

/* Port 2 Port Select Register */

P2SEL &= ~(BIT6 | BIT7);

/* Port 2 Direction Register */

P2DIR = BIT0 | BIT1 | BIT2 | BIT3 | BIT4 | BIT5;

/* Port 2 Interrupt Edge Select Register */

P2IES = 0;

/* Port 2 Interrupt Flag Register */

P2IFG = 0;

/* USER CODE START (section: GPIO_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: GPIO_graceInit_epilogue) */

}

void BCSplus_graceInit(void)

{

/* USER CODE START (section: BCSplus_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: BCSplus_graceInit_prologue) */

/*

* Basic Clock System Control 2

*

* SELM_0 -- DCOCLK

* DIVM_0 -- Divide by 1

* ~SELS -- DCOCLK

* DIVS_0 -- Divide by 1

* ~DCOR -- DCO uses internal resistor

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

BCSCTL2 = SELM_0 | DIVM_0 | DIVS_0;

if (CALBC1_8MHZ != 0xFF) {

/* Adjust this accordingly to your VCC rise time */

__delay_cycles(100000);

// Follow recommended flow. First, clear all DCOx and MODx bits. Then

// apply new RSELx values. Finally, apply new DCOx and MODx bit values.

DCOCTL = 0x00;

BCSCTL1 = CALBC1_8MHZ; /* Set DCO to 8MHz */

DCOCTL = CALDCO_8MHZ;

}

/*

* Basic Clock System Control 1

*

* XT2OFF -- Disable XT2CLK

* ~XTS -- Low Frequency

* DIVA_0 -- Divide by 1

*

* Note: ~XTS indicates that XTS has value zero

*/

BCSCTL1 |= XT2OFF | DIVA_0;

/*

* Basic Clock System Control 3

*

* XT2S_0 -- 0.4 - 1 MHz

* LFXT1S_0 -- If XTS = 0, XT1 = 32768kHz Crystal ; If XTS = 1, XT1 = 0.4 - 1-MHz crystal or resonator

* XCAP_1 -- ~6 pF

*/

BCSCTL3 = XT2S_0 | LFXT1S_0 | XCAP_1;

/* USER CODE START (section: BCSplus_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: BCSplus_graceInit_epilogue) */

}

void System_graceInit(void)

{

/* USER CODE START (section: System_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: System_graceInit_prologue) */

/*

* SR, Status Register

*

* ~SCG1 -- Disable System clock generator 1

* ~SCG0 -- Disable System clock generator 0

* ~OSCOFF -- Oscillator On

* ~CPUOFF -- CPU On

* GIE -- General interrupt enable

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

__bis_SR_register(GIE);

/* USER CODE START (section: System_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: System_graceInit_epilogue) */

}

void WDTplus_graceInit(void)

{

/* USER CODE START (section: RTC_B_graceInit_prologue) */

/* User initialization code */

/* USER CODE END (section: RTC_B_graceInit_prologue) */

/*

* WDTCTL, Watchdog Timer+ Register

*

* WDTPW -- Watchdog password

* WDTHOLD -- Watchdog timer+ is stopped

* ~WDTNMIES -- NMI on rising edge

* ~WDTNMI -- Reset function

* ~WDTTMSEL -- Watchdog mode

* ~WDTCNTCL -- No action

* ~WDTSSEL -- SMCLK

* ~WDTIS0 -- Watchdog clock source bit0 disabled

* ~WDTIS1 -- Watchdog clock source bit1 disabled

*

* Note: ~<BIT> indicates that <BIT> has value zero

*/

WDTCTL = WDTPW | WDTHOLD;

/* USER CODE START (section: RTC_B_graceInit_epilogue) */

/* User code */

/* USER CODE END (section: RTC_B_graceInit_epilogue) */

}

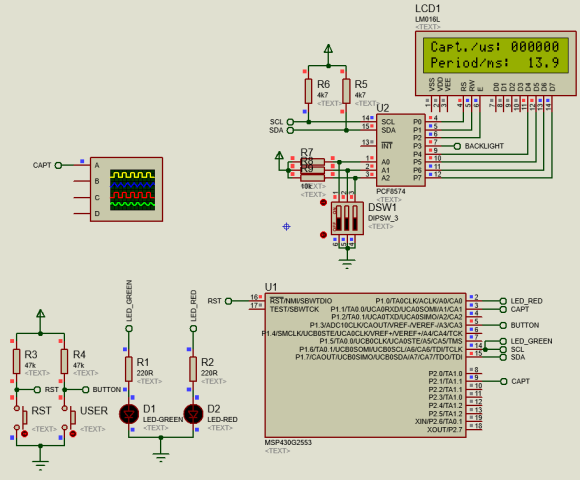

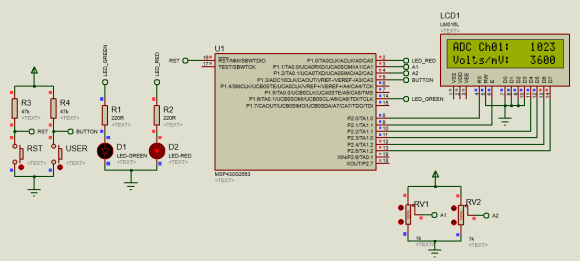

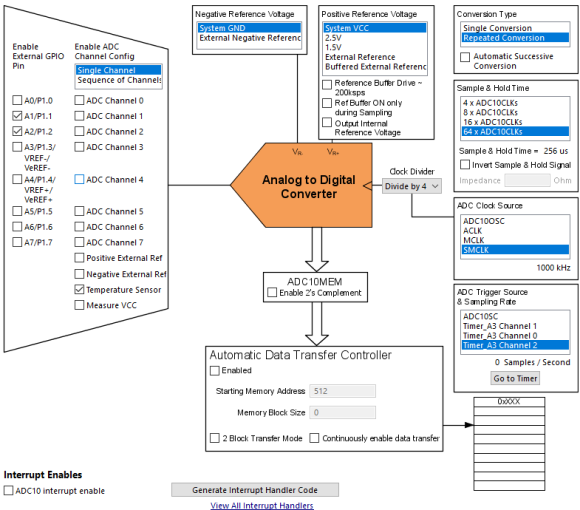

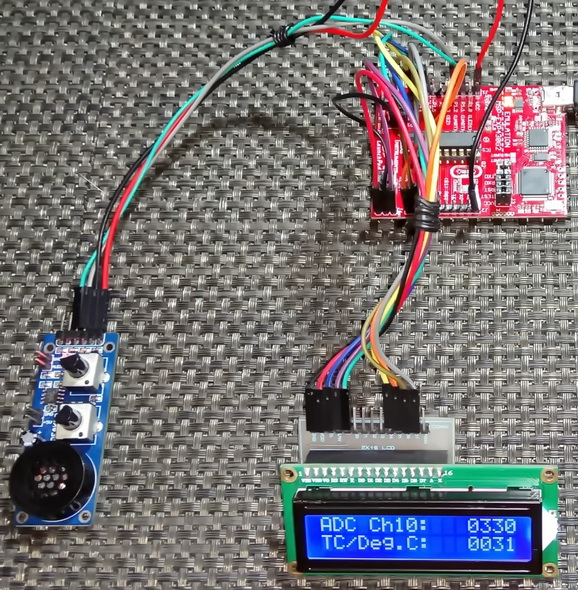

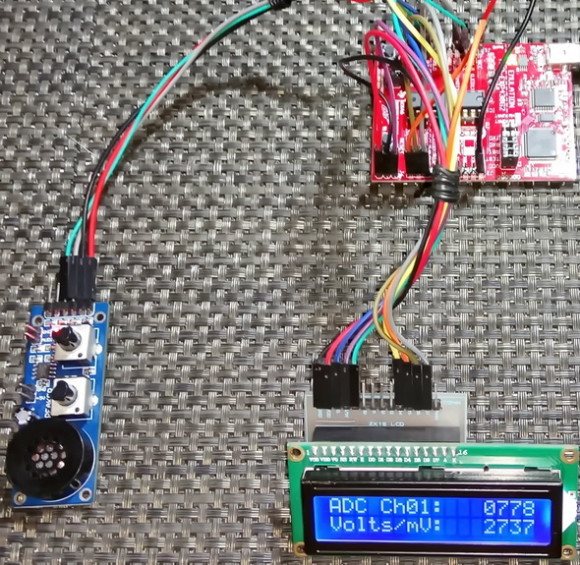

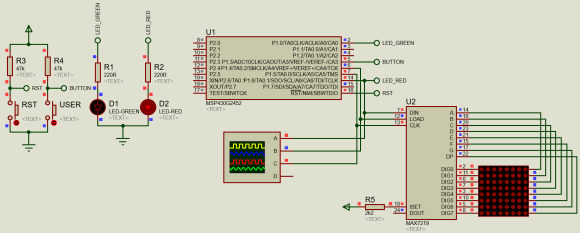

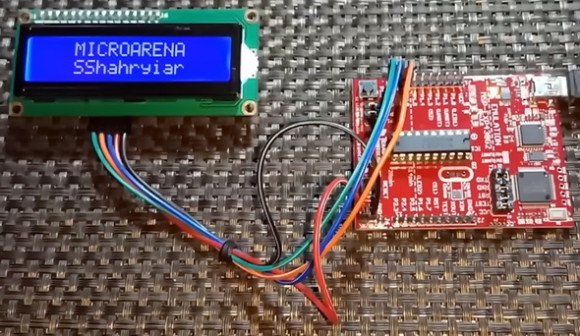

Simulation

Explanation

Hardly there is a thing to explain here. However, there are a few things to note. After having decided the CPU clock frequency, we must edit the following line of the delay header file to make our delays work as much as accurate as possible:

#define F_CPU 8 //CPU Clock in MHz

Software delays are not 100% accurate since they employ wasteful loops of delay cycles which in turn add extra CPU cycles. They are always somewhat close to the actual required value. Delays are also dependent on oscillator accuracy.

Though it is not mandatory but I still recommend that we try to use digital I/Os that have no or least alternate functionalities. This will ensure maximum utilization of limited resources and avoid conflicts as well. Here in this demo, I used P2 port just for that.

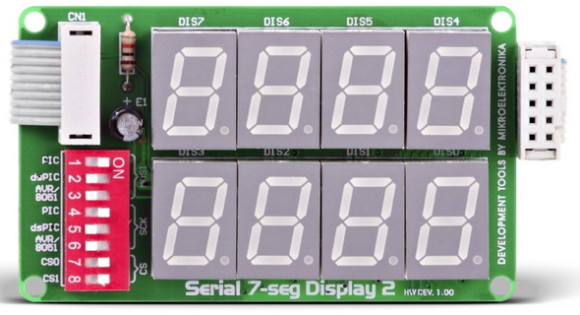

Choosing the right display for a project is often tedious. We have lot of options nowadays ranging from simple LED displays to TFT LCDs. However, considering low power consumption and limited resource availability, it wise to use the simplest form of display. If a project can be completed using seven segment displays, it wasteful and expensive to use a OLED display with seven segment fonts.

LCD displays host their own set of electronics and are prone to Electromagnetic Interference (EMI) and related issues. In many cases, one may end up having a EMI troubled LCD while having the host MCU fully functional and vice-versa. It is always wise to use a short path between a LCD and its host MCU. If needed, use passive low pass antialiasing filters.

Demo

Demo video: https://www.youtube.com/watch?v=sJF8oJPu18s.

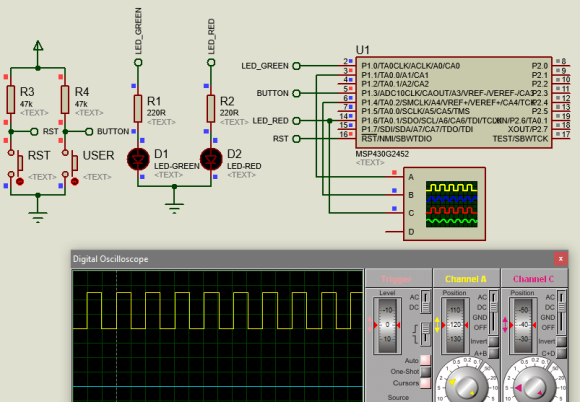

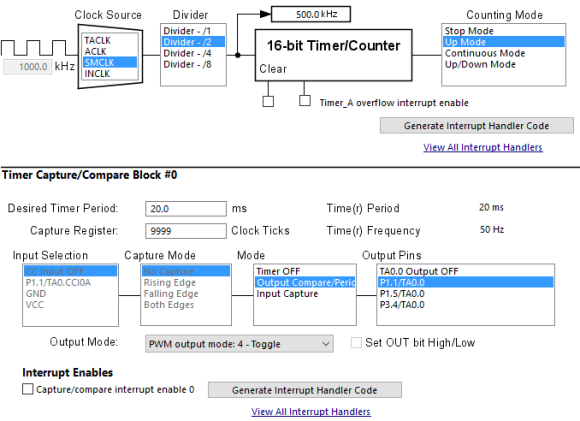

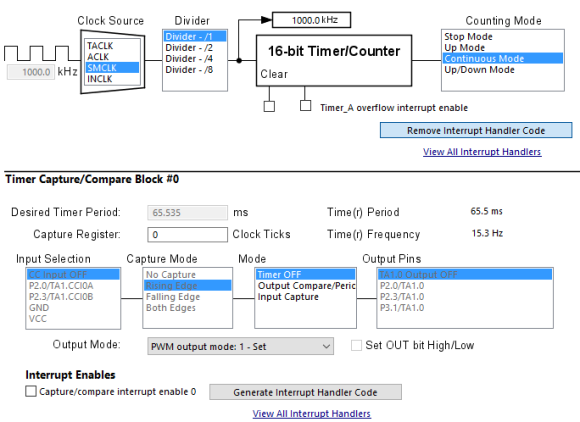

Timer Overview

There are several types of timers in MSP430 micros. These include Watchdog Timer (WDT), Real Time Clock (RTC), Basic Timer 1 and Timer A and Timer B. Timer As and Bs are general purpose 16-bit timers that are suitable for time base generations, pulse width modulations (PWM) and input captures. the other three types have special uses and their names suggest their purposes. All MSP430 devices have at least one Timer A module and a WDT module. Since both are common amongst all devices, we will be studying about them here. Timer As and Bs are almost same. The difference between the two is the presence of some additional features like more Capture/Compare (CC) channels in Timer Bs.

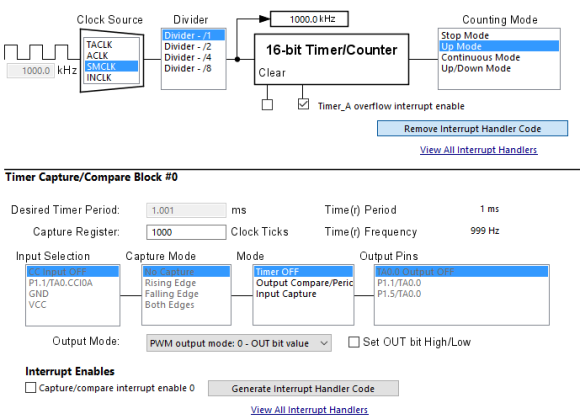

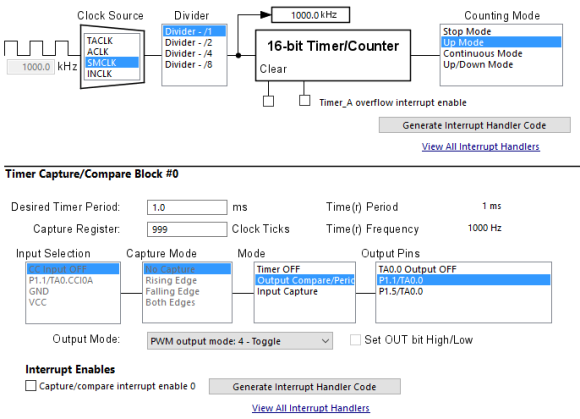

Timer A

In TI’s literature, timers are named like Timer0_A3, Timer_B7, etc. A number can be present right after the word Timer in some case and in other cases, it may be absent. This number is present whenever there are multiple timers of same type in a MSP430 micro. For example, there are two Timer A3s in MSP430G2553 micros and so they are labelled as Timer0_A3 and Timer1_A3. The other number in the timer’s name after the timer type letter denotes the number of CC channels available with it.

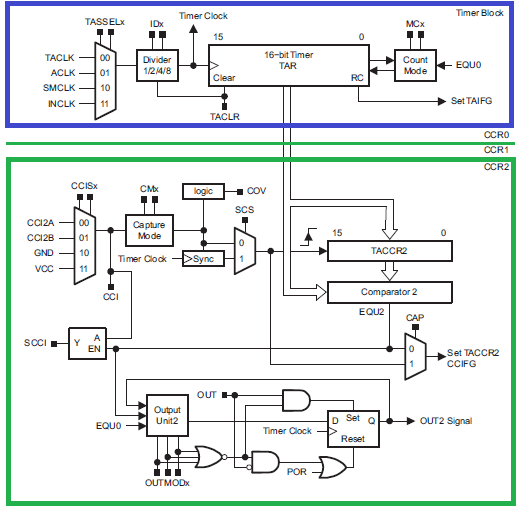

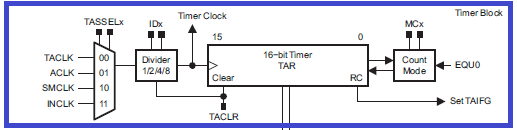

Shown below is the block diagram of Timer A module. MSP430G2452 has one and MSP430G2553 has two Timer A3 modules. Typically, in any micro’s timer we would expect two things – first a counter block (highlighted in purple) and second CC modules (highlighted in green). As we can see the CC channels share the same TAR register and so they share the similar properties.

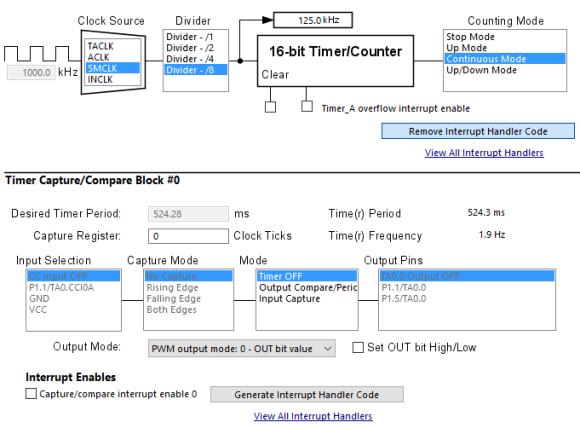

The diagram below shows that clock sources we can use for a Timer A module. It can be clocked with two internal clock sources – ACLK and SMCLK or with two external clock sources – TACLK and INCLK. Actually, INCLK and TACLK are same but one is complementary of the other. These external clocks can be used to make the timer module work as counter.

Next, we have a prescaler to scale down selected clock source followed by the counter block. What’s interesting about MSP430 timers is the counter’s mode of operation. There are four modes of counter operation and these modes define counting direction:

- Stop Mode

It is basically a hold state. All timer registers are retained and the timer is halted.

- Continuous Mode

In this mode, the timer counts up from 0 to top value (here 0xFFFF or 65535 in 16-bit Timer A3) and then rolls over to zero.

- Up Mode

This mode is same as continuous mode except for the top value. The top value of the timer is set by the value in TACCR0.

- Up/Down Mode

In this mode, the timer counts from 0 to TACCR0 value and then rolls back from that value to 0. The period of the timer is twice the TACCR0 counts.

Then we have timer interrupt just as in any other microcontroller.

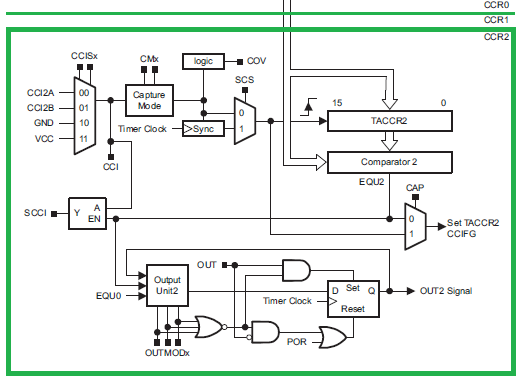

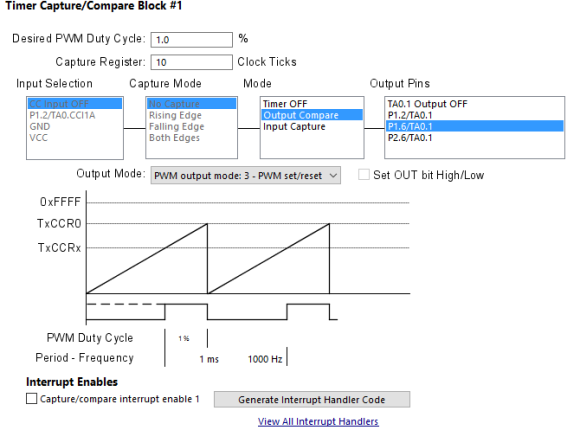

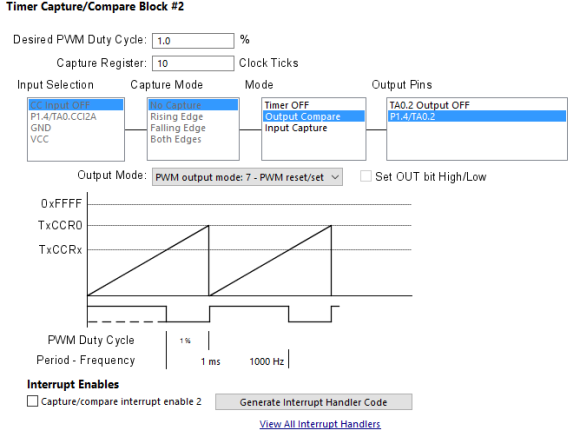

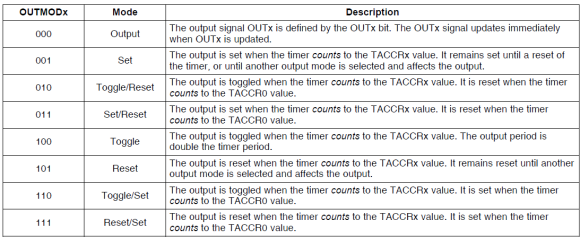

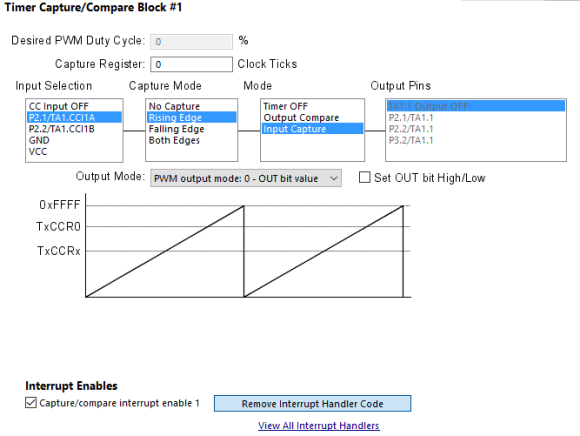

MSP430G2452 has one Timer A3 module and so it has three CC channels. Likewise, MSP430G2553 has six CC channels. When it comes to extreme engineering, TI sometimes seems to overengineer their products. For example, CC channels are not hard fixed to dedicated pins only unlike other micros. Each CC channel has a set of pins associated with it and so they can be remapped if needed. Shown below is the block diagram of a Timer A3 CC channel. The left side of the diagram has all the components for input capture while the right side is intended for compare-match or PWM output. Common to both is the TACCRn block. It is a very important block.

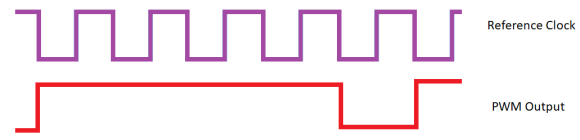

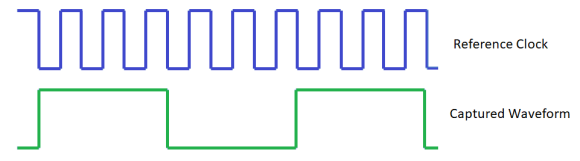

The basic theme of PWM generation as with any microcontroller is to change the logic state of an output pin when the count in it associated TACCR register matches with the count in its timer’s counter register – simply like a binary comparator. This process is called compare-match process. This is exactly the same idea used in MSP430s. Check the rudimentary timing diagram below. For five successive falling edges of the reference clock, the PWM output is high and for one edge, the output is low, resulting in about 83% duty cycle. The reference clock here is actually the timer clock and the comparison is done by comparing the count stored in TACCRn. Varying TACCRn’s count results in duty cycle change.

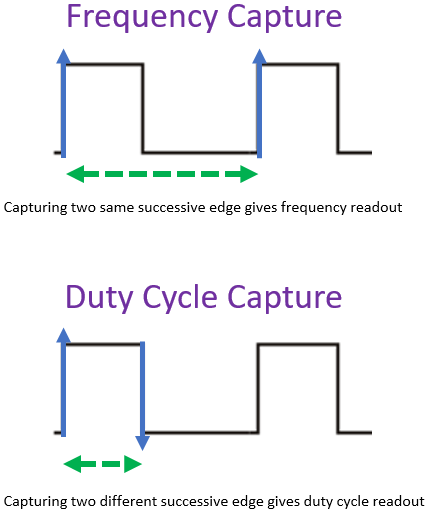

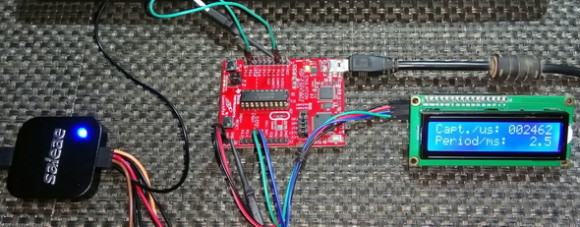

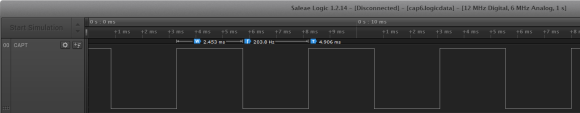

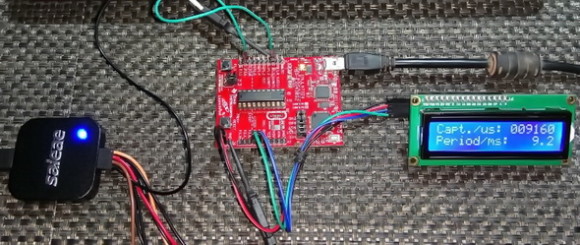

Input capture is somewhat just the opposite of PWM generation. In capture mode, CC channels can be used to record time-related info of an incoming waveform. A timer in this mode can be left to run on its own. When a waveform edge is detected, the corresponding time count of the timer is stored in CC register. With two such consecutive captures, we get a difference in timer’s time counts. This difference can be used to measure frequency if the captured events are alike (two successive rising/falling edges) or duty cycle if the captured events are different (different edges). Again, TACCRn stores the time capture when a capture event occurs.

As an example, check the arbitrary timing diagram below:

Here four falling edges of reference clock (timer clock) is equal to the high or on time of the captured waveform. Since the reference clock’s period is known, we can deduce pulse width.

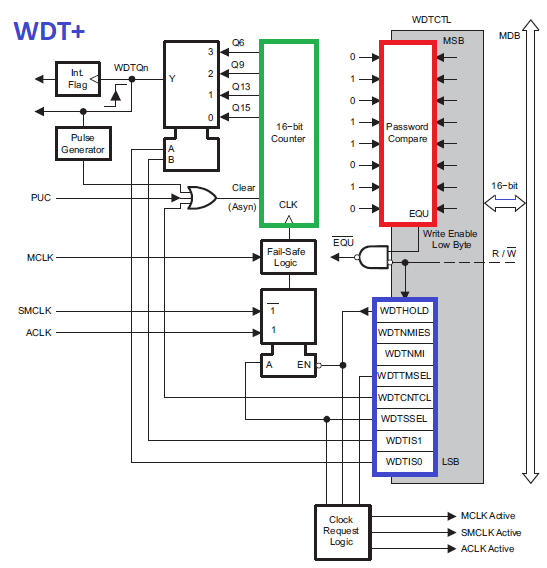

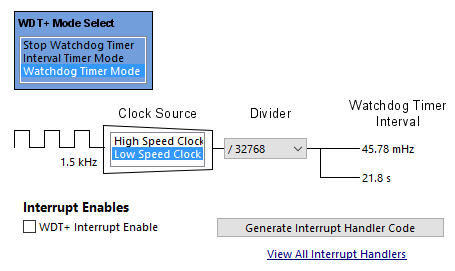

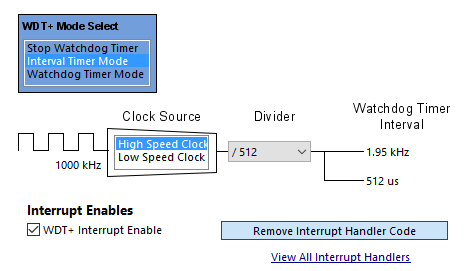

WDT+

WDT+ is a 15/16-bit watchdog timer. It is mainly intended to prevent unanticipated loops or stuck up conditions due to malfunctions or firmware bugs. The concept behind any watchdog timer is to regularly refresh a counter so that the count never reaches a predefined limit. If due to any reason this limit is exceeded, a reset is issued, causing the host micro to start over again.

WDT+ can additional be used as an interval timer just like other timers if watchdog timer functionality is not needed. We can, then, use WDT+ for time-base generations.

WDT+ is password protected and so a wrong password causes it to fail and reset immediately. This is the red box in the diagram above. Whenever we need to change anything related to WDT+, we have to enter the correct password which is 0x5A00. WDT+ consists of a 16-bit counter (green box) but we don’t have access to it. The purple region consists of WDT options. The red and the purple boxes make up Watchdog Control (WDTCTL) register and this is what we are only allowed to code.

Free Running Timer

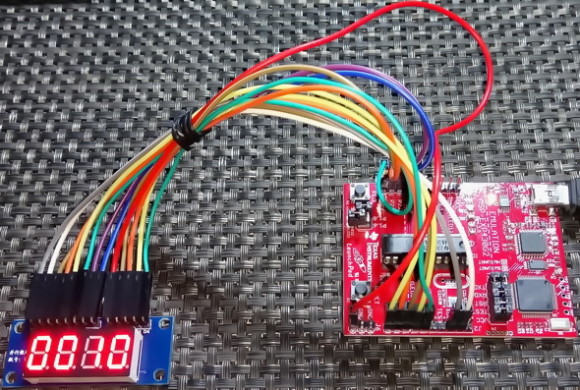

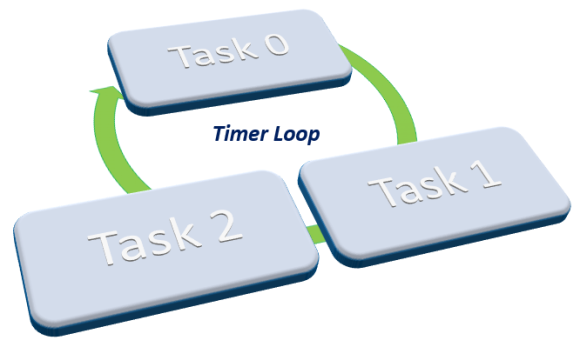

Free running timers are useful in many cases. Free running timers can be used as random number generators, time delay generators, instance markers, etc. Consider the case of time delay generation for instance. Rather than using wasteful CPU-cycle dependent software delay loops, it is much wiser to use a hardware timer to create precise delays and timed events. In terms of ideal coding, no task should keep CPU busy unnecessarily nor should it keep other tasks waiting for its completion. Best coding and design are achieved if things are arranged in such an orderly way that that there is almost no wastage of any resource at all.

By free-running what I really mean is we start a timer at the beginning of our code and keep it running without timer interrupt. We just take note of its counter. Here we will see how to use Timer_A3 like a free running timer and we will use it to blink Launchpad board’s LEDs.

Code Example

#include <msp430.h>

void GPIO_graceInit(void);

void BCSplus_graceInit(void);

void Timer0_A3_graceInit(void);

void System_graceInit(void);

void WDTplus_graceInit(void);

#pragma vector=TIMER0_A1_VECTOR

__interrupt void TIMER0_A1_ISR_HOOK(void)

{

}

void main(void)

{

/* Stop watchdog timer from timing out during initial start-up. */

WDTCTL = WDTPW | WDTHOLD;

/* initialize Config for the MSP430 GPIO */

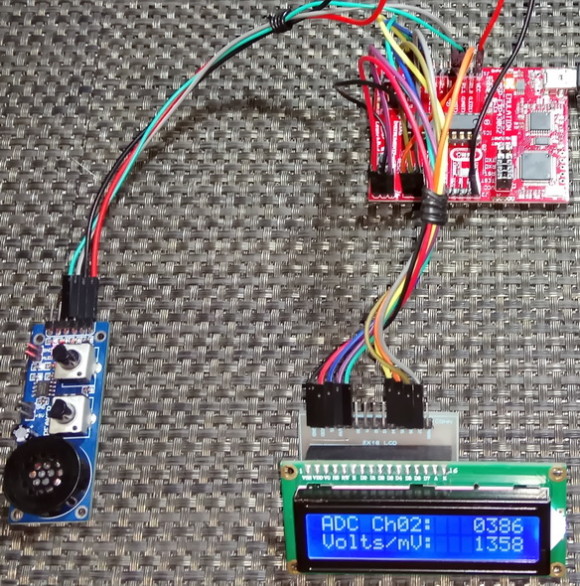

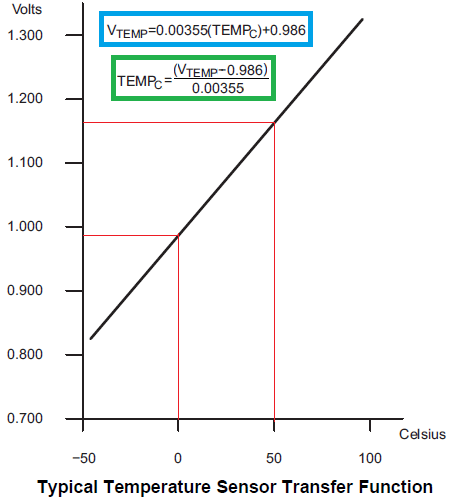

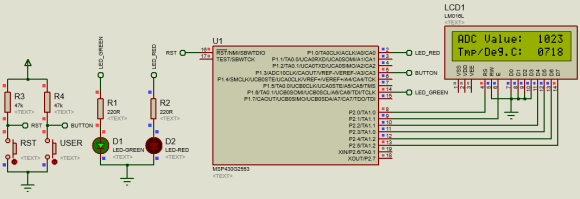

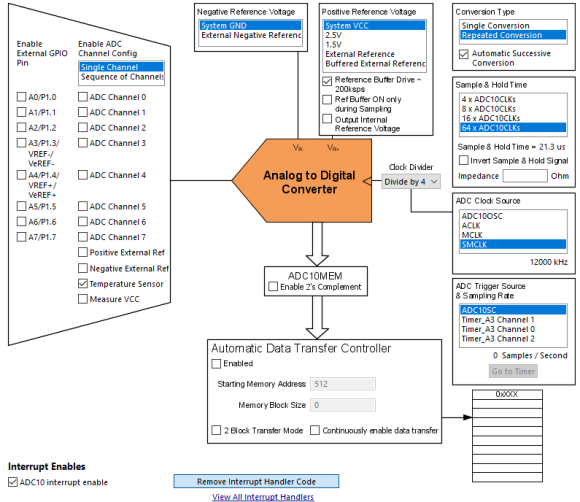

GPIO_graceInit();